Hic Draconis

This chapter is a work in progress. There'll be broken references, speling mistakes, badly written copy and some details missing altogether. Tread lightly! Oh, and yes. It's immense.The CFT minicomputer is intended to be similar to a 1960s minicomputer, and it could never be similar enough without a programmer's front panel: a front panel that can boot and program the computer.

The front panel allows the state of the computer to be inspected and modified. State inspection is made possible via a number of lights corresponding to the state of the processor's registers in binary. State modification is via a number of switches which control the operation of the computer's main units and allow for user input to enter the computer.

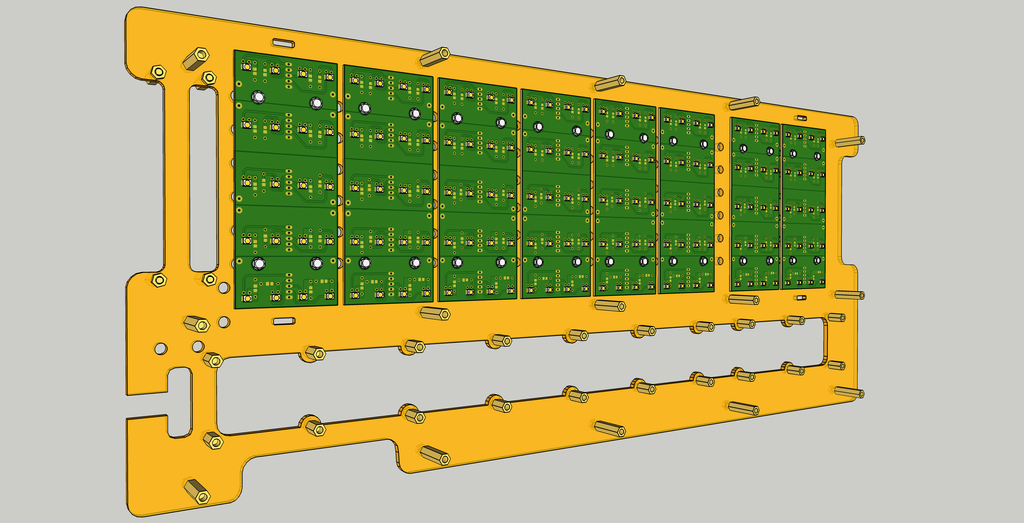

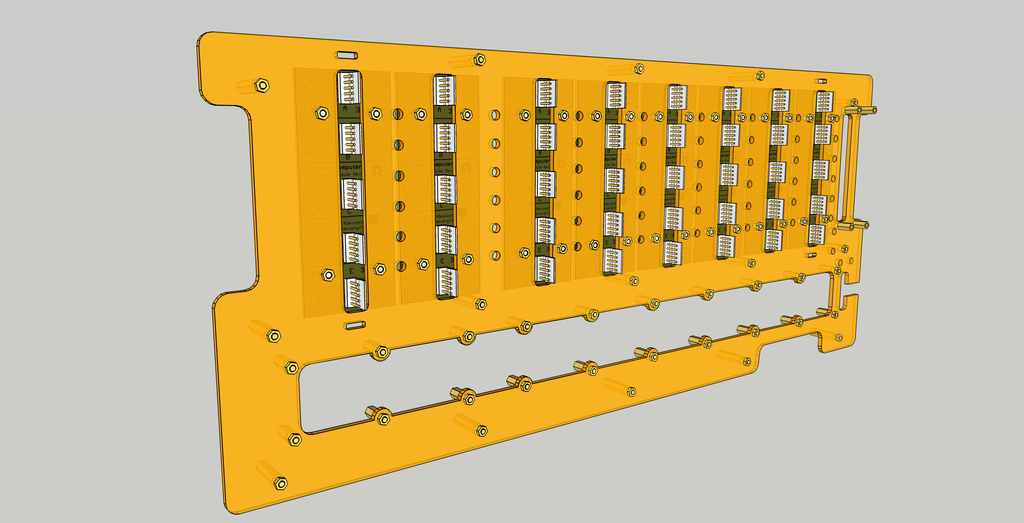

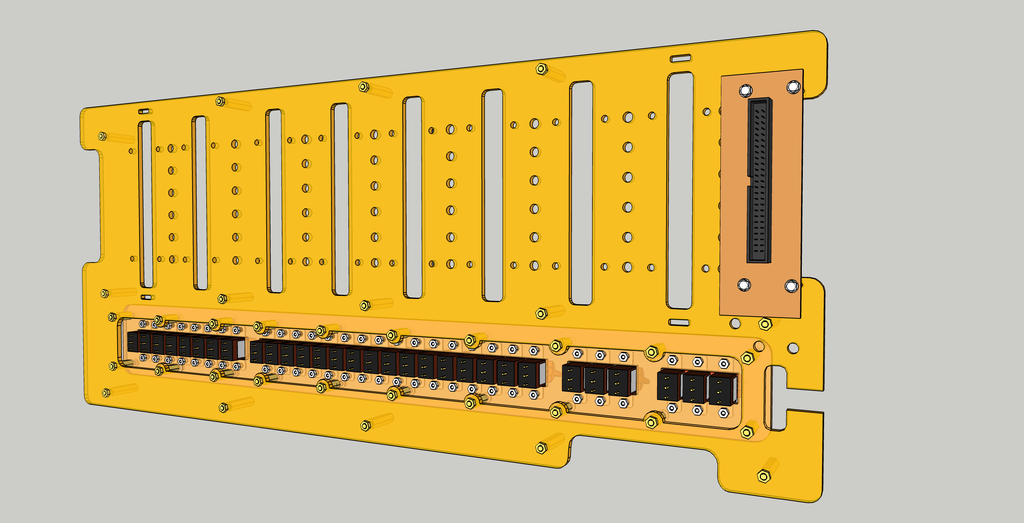

The Debugging Front Panel is a very large sub-project, replacing both the early Programmer’s Front Panel and Debugging Board. It is built on two boards providing a three-way interface between the CFT processor, the front panel, and an optional computer used to automate testing the CFT. The computer may be replaced by a human when running custom diagnostics or even using the front panel remotely.

The DFP forms a triple interface between the CFT computer, the front panel, and a remote test operator, which can be a computer or human.

On the computer side, the DFP behaves as a processor extension. It connects to the Control Bus like processor boards do; it connects to each processor board's front panel interface which mostly outputs register values; and it connects to the Expansion Bus so it can be treated like a peripheral and also control peripherals itself.

On the front panel side, the DFP is connected to most of the lights on the front panel. It directly controls some (but not all of them). It is also connected to all the front panel switches.

On the serial port side, the DFP provides two services. A Virtual Front Panel, a superset of the test harness features of the defunct DEB board: this can read and manipulate the state of the computer, front panel lights and switches, and receive test results from the computer via the DFP controller. The second service is a (slow) Virtual Console, which is a simplistic serial terminal the computer can use to interact with a user.

You can see the integration of computer, panel and serial port in action: in this this video, I toggle in a simple program to demonstrate some of the processor. The video shows the front panel being used to program and operate the computer. The serial port interface shows the state of the switches and memory and is used to verify the work. When the program finally runs, the computer uses the DFP to register successes and display data while the panel lights show its state.

If this reminds you of the unholy love child of 1970s monitor software and modern server management, it's because it's been heavily influenced by both. Monitor software (including the one in the Apple II, AIM-65 and the ‘M’ in ‘CP/M’) came about when computers stopped having physical front panels—they bridge the world of toggle switches and command line operating systems). And of course server management hardware provides a command-line interface to diagnose and control a modern computer.

There's another precedent though: many minicomputers and even workstations used an auxiliary processor for diagnostics. For example, the Xerox Star's IOP board is responsible for the computer's early diagnostics. It even initialises the microcode (held in RAM) and makes the computer able to boot. After boot, it stays around and behaves like an interface to the slower devices like the keyboard and mouse. And to make it even more similar, it's an MCU-baseddiagnostics/testing/peripheral board used to bring up a microcoded processor made out of discrete chips.

C3.1. Subsystems and Facilities

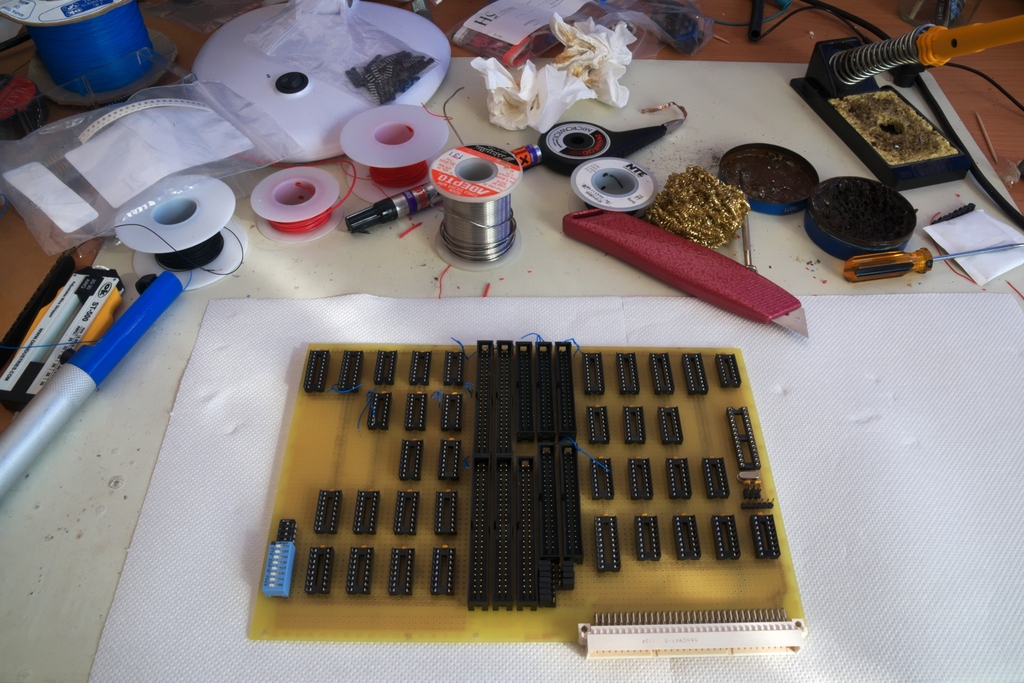

The device is made up of more parts and sub-assemblies and cabling than any other CFT sub-project. There are numerous facilities, both physical and logical.

The eponymous front panel, the traditional input/output device of mini-computers.

It has 160 lights, though many are left unconnected and some are meant for future expansion. 145 lights are currently installed, wired or assigned future functions.

There are switches to control, debug and test the computer.

There are some switches to control the front panel itself.

Another 16 switches are directly connected to the SR, which can be read by both the computer and front panel. They are the computer's sole input device.

A key lock switch to control power.

A key lock switch to lock the panel. I put those in because they make the whole thing look more realistic and professionally done. Many mini-computers had them, after all.

An internal bank of DIP switches to allow the user to set non-volatile preferences. These depend entirely on the CFT's ROM for interpretation.

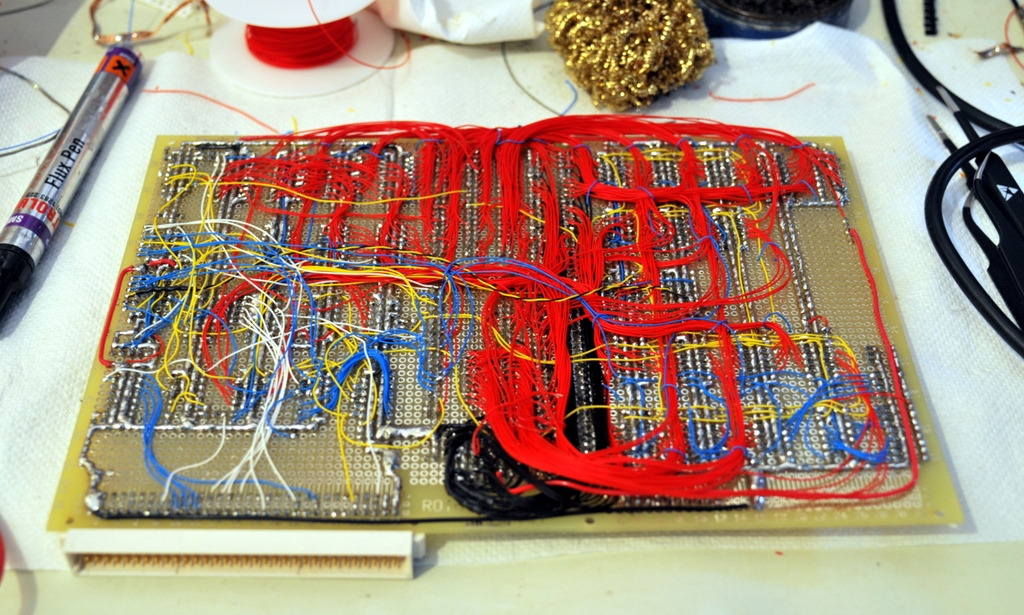

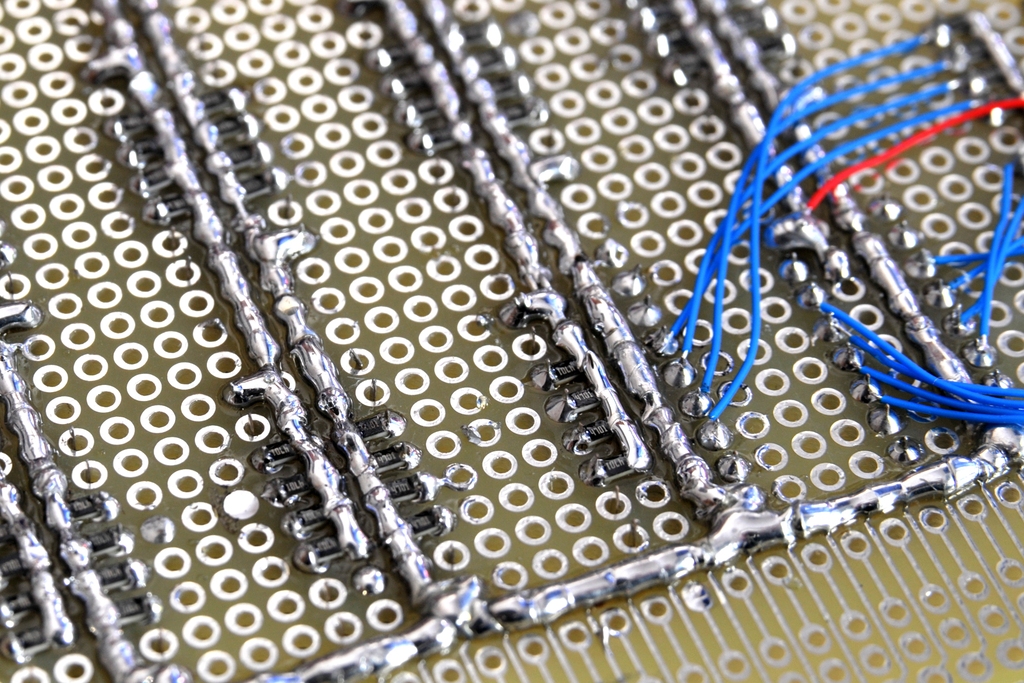

Wiring facilities that route the processor boards' front panel connectors to the correct front panel lights. These involve a large number of connectors and an even larger quantity of wiring.

More wiring facilities to route signals from add-on cards to the lights, including the MBU and IRC.

A debouncing facility for the switches controlling computer functions and programming.

Mutual lock-out for control switches so that multiple panel operations can't be started simultaneously by mistake. This also includes locking out most panel operations when the panel lock is activated.

An optional auto-repeat facility for the Step/Microstep switch. This is useful in debugging and saves wear on the switch.

A 16-bit Output Register (OR) which displays its value on the front panel MFD.

A sequencer to perform memory and I/O space reads and writes, and optionally increment the address after each cycle. This provides a total of eight bus functions, assigned to four double-throw toggle switches on the front panel.

A switch to configure the optional MBU for either bare-metal operation (the computer starts halted, and the entire 64 kWords of memory is RAM), or turn-key operation (ROM is mapped to the top 32 kWords, and the computer starts in the run state, like all modern computers).

A switch to issue panel-initiated interrupt requests for interacting with computer programs.

A slow clock generator capable of providing two slow clock rates, in addition to the rate provided by the CFT processor's own clock generator. These are useful for debugging and demonstrations.

A state machine used to halt the computer at the appropriate part of the processor cycle. This state machine is also used for stepping and micro-stepping.

When the DFP was merged with the DEB board, a number of additional facilities were added, and many were merged together.

C3.2. Standalone Mode

You may see some references to this. Initially, the DFP was meant to operate the computer's buses and peripherals with the precious processor boards unplugged. This would let me test new peripherals without risking damage to the most complex (and thus most difficult to diagnose) components of the system.

Eventually, three things became apparent. One, the DFP was a very good contender for the most difficult component to diagnose problems with. In fact, I'd rather delve into the Processor Boards because at least they're nice and neat. Two, once you have some basic rules down, it's hard to damage the ICs. Three, the processor boards provide some facilities (like bus hold and conditioning, wait states, write strobes, etc.) I'd rather not replicate on the DFP. So the DFP and processor can't operate independently anyway, and Standalone Mode went away. The code is still there in the DFP firmware, and some messages (like those that indicate a processor was found) still hint at how it all was.

C3.3. The Front Panel

The front panel allows the state of the computer to be observer via a number of lights. It also allows the state of the computer to be modified using a number of switches. The CFT front panel is expected to provide a number of services.

It provides a means of testing most of the computer's individual units on their own. With some rewiring or reconfiguration, all of the computer's features can be tested.

It allows microcode to be inspected and debugged.

It allows the computer to be programmed without a ROM. A front panel was historically the only built-in means of programming a minicomputer, and in many cases was the only way the computer could be booted up.

It helps debug software and hardware by allowing the computer to be stopped, its state inspected and perhaps changed, and then resuming execution.

It allows the state of the running computer to be inspected with varying degrees of success. The human eye is incapable of registering individual light pulses at more than around 20 Hz, seeing varying intensities instead. A trained operator can glean plenty of information from these patterns.

It provides the computer with a simple input device (sense switches) and output device (the Output Register).

It also provides a simple (if very slow) serial port for early debugging of interactive features, before the TTY board is built.

C3.3.1. Layout of the Front Panel

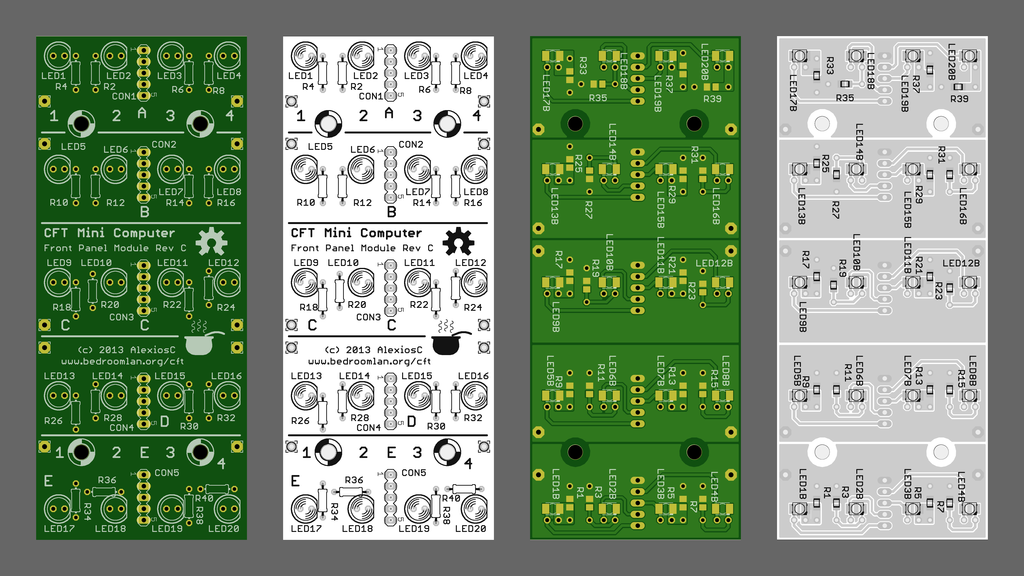

The front panel displays up to 177 bits of information on 145 lights arranged in two to three columns by five rows. Some lights serve multiple purposes, and others are not yet tasked. It also includes 30 toggle switches that modify the state of the computer and the front panel itself. There are also two key locks: one to control power and one to lock the front panel itself.

All lights and switches displaying multi-bit quantities are arranged with the most significant bit to the right, in the conventional notation of binary numbers. Bit numbers start at 0, which is the least significant bit or rightmost light. This follows the conventional notation of powers-of-two.

The ninth iteration of the front panel's design, featuring 145 lights, 30 switches and two key locks.

C3.3.2. Evolution of the Front Panel Design

Like everything about the CFT, the front panel has gone through an insane number of revisions. Like everything about the CFT, the front panel wasn't created in a vacuum, either. I was inspired by the front panels of various PDP machines, but finally found my muse in John Doran's D16/M—which also provided some much needed tips on how to construct a beautiful front panel.

Front Panel version 1: a 6U monstrosity with six rows of light, two rows of switches, a single key switch, and the original, cheekily retro logo.

Front Panel version 2: the switches are more compact now.

Front Panel version 3: reorganises the lights to fit the UCB extension indicators.

Front Panel version 4: the first 4U version, with a single row of switches, two key switches and a more compact arrangement of lights.

Front Panel version 5: a few minor changes to the light legends to accommodate newer versions of the Microcode.

Front Panel version 6: the key locks have moved so the keys don't dangle over the toggle switches. The panel is centred. The instruction set cheat sheet under the switches reflects recent Microcode updates. New logo!

Front Panel version 7: legend changes.

Front Panel version 8: again, minor incremental changes.

Front Panel version 9: the logo has moved to the top right corner. Mock switches in roughly the correct colours have been added to the diagram.

C3.3.3. Console Lights

The 144 console lights are arranged in two to three columns and five rows, arranged on a 32×5 grid. The centre of the panel represents various 16-bit values, usually registers. The left side shows smaller vectors and individual bits of state. The right side is reserved for peripherals.

Hey, No Cheating Now!

Yes, there's an Microcontroller Unit (MCU) on board. However, nearly all of the lights on the front panel are connected directly to the Processor Boards. the MCU can sample their values, but it doesn't control them. This is why the back of the front panel is such a rat's nest of cables. There are two exceptions: the Output Register, controlled entirely by the MCU(naturally, since it's a peripheral provided by it), and the Run and Stop lights, which are outputs from the Run Control State Machine which is controlled by the MCU too.C3.3.3.1. Micro-Instruction Control Vector

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

This row of 24 lights displays the current output of the microcode store, and the current micro-operation performed by the processor. A light being on indicates an asserted signal: active low signals are inverted to make the display clearer to humans.

C3.3.3.2. Memory Bank Unit

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

This row of 8 yellow lights displays the currently selected memory bank (address bits 13–20). It is driven by the MBU. An additional green MBENlight (leftmost on the third row from the top) indicates that the MBU's soft memory mapping is enabled. When on, the leftmost light indicates the ROM is being accessed. For more information, please consult MBU.

C3.3.3.3. Program Counter

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

This row of 16 red lights displays the current value of the Program Counter (PC).

C3.3.3.4. Flags

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

This row of five green lights displays the state of the processor's flags: the Negative flag (N), Zero flag (Z), Overflow flag (V), Interrupt flag (I) and Link register (L).

C3.3.3.5. Accumulator

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

This row of sixteen red lights displays the current value of the Accumulator (AC).

C3.3.3.6. State

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

This row of seven lights displays major and minor states of the processor. States include Reset, Run, Stop, Wait State, Fetch, Execute states, as well as the Interrupt state, which lights to indicate an interrupt has been received but not yet serviced.

Of these lights, the Run and Stop lights are controlled by the MCU since it controls running, stepping and stopping of the computer. The MCU blinks the Stop light when it encounters a critical fault during self-diagnostics or processor diagnostics at power on. If the Stop light is blinking, it's a clear indication the computer isn't healthy enough to be allowed to come out of reset.

C3.3.3.7. Output Register, Data Register and Micro-Address Vector

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

This row of sixteen lights is an Multi-Function Display (MFD) that can display the value of the front panel's Output Register (OR), the Data Register (DR), or the current Micro-Address vector. The latter represents bits 0–14 of the current address of the Microcode store. The value of the Microcode Store at this address is displayed on the top row. Please note that this is a 15-bit vector, and the rightmost light is not used. Some bits, corresponding to active-low signals, are inverted. These are not inverted to ease reading, since the value is meant to be interpreted as a Microcode Store address.

The Output Register is controlled entirely by the MCU since it's a peripheral provided by it. What appears on the MFD, though, is set by two bits output by the two poles of the OR/DR/µADDR Vector switch (decoded by a 74HC138 3-to-8 decoder—to provide sanity checking and indirectly deal with bounces and switch noise).

C3.3.3.8. Microcode Bank

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

These four lights represent bits 15—18 of the current Micro-Address vector, if the optional MBU is installed. Under most normal circumstances, these lights should be off.

C3.3.3.9. Instruction Register

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

Sixteen lights display the current value of the Instruction Register (IR). Different colours indicate different fields of the instruction.

C3.3.3.10. Interrupt Requests and Enabled Interrupts

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

Sixteen lights in two rows display the state of each of the eight interrupt lines of the optional IRC. Enabled interrupts are shown on the top line, while requested interrupts are shown below.

C3.3.3.11. Spare Lights

●●●●●●●●●●●●●●●●●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●○●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ●●●●●●●○●●●●●●●●●●●●●●●●○●●●●●●●● ○○○●●●●○●●●●●●●●●●●●●●●●○●●●●●●●●

Sixteen lights in two rows are available for peripherals to attach to. Devices such as hard drives and network interfaces that display their state using LEDs may do so here. Future iterations of the front panel will assign values to at least some of these.

C3.3.4. Switches

There are 30 switches and two key locks on the front panel. Many switches perform two actions depending on whether they are pushed up or down.

The power lock controls the computer's power supply. It may be locked in the on or off position.

The panel lock controls access to the rest of the front panel. The panel may be open or locked out. When in the locked out position, most panel functions are unavailable. This is useful for displaying the computer, and for security.

The remaining 30 toggle switches are split into four groups: run control and panel settings, the Switch Register (SR), and programming functionality.

C3.3.4.1. Run Control

The Run Control and Panel Settings switch group is located on the bottom row of switches, below the Switch Register switches. It comprises three momentary action switches with six functions. Switches may be pushed up or down momentarily to activate their corresponding functions.

C3.3.4.1.1. The Reset/Start Switch

Actuated upwards (RESET), this switch resets the computer. If the computer is halted, it will go through the reset sequence and remain halted. When the switch is pushed downwards (START), the computer will reset and start running if stopped. (this combines the RUN and RESET functions)

C3.3.4.1.2. The Run/Stop Switch

Actuated upwards (RUN), this switch causes the computer to leave the Halt state and start executing code (Run state). If actuated downwards (STOP), the computer finishes executing the current instruction and stops, entering the Halt state.

C3.3.4.1.3. The µStep/Step Switch

This switch has no effect unless the computer is halted. Actuating it upwards (µSTEP) causes this computer to perform a single microstep. This is useful for diagnosing microcode issues. Pushing the switch downwards (STEP) causes the computer to step through one whole machine instruction. The processor will halt at the end of the instruction, so that the IRlights will display the instruction that just ran and the PC lights will show the address of the next instruction to execute.

C3.3.4.1.4. Fast/Slow/Creep

This switch has three positions controlling the CFT processor's clock speed. In FASTmode, the computer operates at the fastest available speed, typically 4 MHz. In SLOWmode, the computer operates at a speed that allows program execution to be inspected, typically 80 Hz (approximately ten instructions per second). In CREEP mode, the clock slows down to 8 Hz, so microprograms can be seen running.

C3.3.4.2. Panel Control

The Panel Control group configures the front panel.

C3.3.4.2.1. Lights On/Off

This switch has two positions. In the ON position, all panel lights are operational. In the OFF position, many of the panel lights are disabled to avoid visual clutter while the computer is running. The groups of lights that can be disabled are configurable using blocks of jumpers on the Front Panel Controller Board.

C3.3.4.2.2. OR/DR/µADDR Vector

This three-position switch controls what is displayed by the 16 Multi-Function Display (MDF) lights. In ORmode, the Front Panel's OR is shown. In DR mode, the DR is displayed. In µADDR mode, the Microcode Address is shown.

C3.3.4.3. The Switch Register

The Switch Register comprises sixteen switches. Together, they provide a 16-bit value used as input by the front-panel itself as well as the computer (sense switches, ready using the LSRextended instruction. Switches pushed up represent set bits (binary 1). Switches pushed down represent clear bits (binary 0).

C3.3.4.4. Programming Switches

The programming and state modification group is the rightmost group of switches. It comprises seven momentary action action switches and one on-on toggle switch.

C3.3.4.4.1. The SR → IR and SR → PC Switch

Pushed up, this switch copies the value of the SR to the IR. This modifies the instruction being executed. The computer must be halted. Obviously, changing the IR changes the microprogram being executed. It should, ideally, be done before the Execute state is reached, otherwise the microcode-level side-effects are difficult to gauge. This switch is most useful in debugging microcode issues.

Pushed down, the value of the Switch Register is copied to the PC. The computer must be halted for this. This switch is often used when programming or debugging via the front panel. It sets the address of all subsequent data entry (or examination) via the front panel.

Address Weirdness

For lack of available registers, modifying the PC is the way front panels often did it in the days of olde. The DFP's test interface (over the serial port) has a separatea register which allows examining and modifying memory without touch the computer's registers. That register isn't visible on the front panel lights, though, so modifying the PCwas the easy way. Why keep things too simple though? Actuating the SR→PC switch will also set the a register. This keeps the front panel and serial interface in sync, and interoperable. You can set an address via the switches, then dump memory via the serial interface.C3.3.4.4.2. The SR → AC Switch

Activated either up or down, this switch copies the value of the SR to the AC. The computer must be halted for this.

C3.3.4.4.3. The Memory Write and Memory Write Next Switch

Pushed up, the current value of the SR is stored to the memory address indicated by the PC. Pushing the switch down performs the same task, but increments the PC afterwards. The computer must be halted for this. If this switch is kept down, it auto-repeats in three stages of increasing speeds. This allows large areas of memory to be filled quickly.

C3.3.4.4.4. The Memory Read and Memory Read Next Switch

Pushed up, the value at the memory address indicated by the PC is read into the AC, and obviously displayed on the front panel. Pushing the switch down performs the same task, but increments the PC afterwards. The computer must be halted for this. If this switch is kept down, it auto-repeats in three stages of increasing speeds. This allows large areas of memory to be read and visualised quickly.

C3.3.4.4.5. The I/O Write and I/O Write Next Switch

Pushed up, the current value of the SR is output to the I/O space address indicated by the PC. Pushing the switch down performs the same task, but increments the PC afterwards. The computer must be halted for this. If this switch is kept down, it auto-repeats in three stages of increasing speeds. This allows large areas of I/O space to be filled with the same value quickly. Care should be taken when doing this, as it can have very unexpected effects.

C3.3.4.4.6. The I/O Read and I/O Write Next Switch

Pushed up, the value at the I/O space address indicated by the PC is read into the ACand displayed on the front panel. Pushing the switch down performs the same task, but increments the PC afterwards. The computer must be halted for this. If this switch is kept down, it auto-repeats in three stages of increasing speeds. This allows large areas of I/O space to be read and visualised quickly.

C3.3.4.4.7. RAM Bank/ROM Bank

This is a two position switch. In the RAM BNK position, the MBU's initial hard mapping provides 64 kWords of RAM and no ROM. When powered on, the computer will reset to the Halt state, allowing a program to be toggled in. In the ROM BNK position, the MBU's initial hard mapping provides 32 kWords of RAM and 32 kWords of ROM. The computer powers up in Run mode, allowing the boot code in ROM to be executed. This switch does nothing if the MBU's soft mapping has been enabled (the green MBEN light is on).

C3.3.4.4.8. IFR1/IFR6 Switch

If the optional IRC card is installed, this switch can signal Interrupts Level 1 and 6 to the computer. This may be used for debugging or asynchronous input. If the IRC card isn't present, a jumper on the DFP board makes IFR6 work with the CFT's single interrupt source. IFR1 won't work without the IRC card, though.

C3.3.5. Using the Front Panel

This section describes how to use and program the computer via the front panel.

C3.3.5.1. Power

Insert the power key in the power key switch. Turn the key clockwise to the ‘on’ position. The computer activates, performs power supply diagnostics (the DFP also performs its own power-on diagnostics at this point). The processor then goes through a reset cycle, and:

if the RAM BNK/ROM BNK switch is in the RAM BNK position, the processor halts. The STOP light should illuminate at this point, and the PC will indicate a binary address of 1111·1111·1111·0000, or FFF0.

if the RAM BNK/ROM BNK switch is in the ROM BNK position, the RUN light illuminates and the processor starts executing the boot code in ROM.

C3.3.5.2. The Panel Lock

When the panel lock is activated, access to the physical front panel is restricted. Only the SR, and IFR1, and IFR6 switches are operational. The panel may be locked using the physical front panel lock, or via the lock command on the DFP Console.

The physical and logical panel locks are in a mutual override relationship. Any change to either changes the state of the panel lock. So, if the panel has been locked via the DFP console and the key switch is in the unlocked position, it will be necessary to operate the key switch twice (move from unlock to lock, then back from lock to unlock) in order to unlock the panel.

C3.3.5.3. The Switch Register

The SR is made up of 16 switches, colour-coded in four groups of four (nybbles). A legend below the switches shows bit numbers (exponents), hexadecimal bit values (powers of two) and octal bit values (this could change to decimal prior to panel construction, which is slightly more useful on the CFT). A mnemonic of the 16 base instructions of the CFT is also provided.

Clear bits by pushing switches down. Set bits by pushing switches up. Simple enough.

The DFP monitors these switches for changes and sets the SR whenever a change to any of the switches occurs. This is done because the SR may also be set from the DFP Console (mutual override). If this has been done, to set the SR back to the value on the switches, it is necessary to toggle any switch twice.

C3.3.5.4. Boot or Reboot from ROM

With the computer powered up, move the RAM BNK/ROM BNK switch to the ROM BNK position and depress the RESET or START switch. The computer boots from ROM address FFF0 and begins execution.

You may now secure the front panel by turning the panel key switch to the LOCKED position.

C3.3.5.5. Resetting the Computer

With the key switch in the UNLOCKED position, depress RESET or START. The computer resets. If the computer is halted, START will also set it running.

C3.3.5.6. Toggle in Boot Code

Ensure the computer is freshly powered up and halted, or halted and reset.

Set the SR for a low value such as 0000·0100·0000·0000 or 0400. (one kWord from start of memory). Depress SR→PC. The PC will change to the address selected on the SR.

Set the SR to the opcode of the first instruction of bootstrap code. Depress MEM W NEXT. The value of the SR is written to the memory address of the PC, and that memory address is incremented. Repeat this step as required until all code has been entered.

Reset the SR to the initial address of the bootstrap program. Depress SR→PC. The PC will be set to that address.

Depress RUN. The computer starts execution of the code from the specified address.

You may now secure the front panel by turning the panel key switch to the LOCKED position.

C3.3.5.7. Examining Memory

Ensure the computer is powered up and halted.

Set the SR to the start of the memory area you need to examine. Depress SR→PC. The PC will change to the address selected on the Switch Register.

Depress the MEM R NEXT switch. The value at the selected memory address is loaded into the AC and displayed on the front panel. The memory address is incremented. Repeat this step as many times as necessary.

C3.3.5.8. Halting the Computer Forcibly

With the key switch in the UNLOCKED position, depress STOP. The computer finishes its current instruction and halts. The RUN light will extinguish, and the STOP light should turn on.

C3.3.5.9. Debugging with the Front Panel

The front panel may be used to interrupt normal computer operation and inspect or modify its state for debugging purposes. The computer can then resume operation. The user should, however, be aware of a number of considerations when using the front panel to do this:

Operating the STOP switch halts the computer immediately after the next instruction is fetched, and before its execution starts. At this point, the µSTEP or STEP switches may be operated repeatedly.

Using the SR→PC switch to set the address for examining or modifying code also modifies the PC. When the computer resumes operation, and after execution of the current instruction, the processor will jump to the address set via the front panel. If this is not desired, the user must note the value of the PC and manually restore it before continuing.

Using the memory and I/O functions also cause the MAR to change. This is safe to do when using the STEP switch, but be aware of it while debugging microprograms!

Obviously, modifying the IR, memory, or I/O devices can have unexpected side effects and can cause the program to fail when it's resumed. The front panel is powerful, but can be too powerful if not used wisely!

C3.4. The Debugging System

The DFP allows a remote computer to automatically and programmatically control the CFT for debugging and testing purposes, effectively providing a virtual front panel. This interface may also be operated by a human. It allows facilities more advanced than the front panel's and is an integral part of constructing the CFT, as it allows for automated unit testing and detailed diagnostics.

C3.4.1. Attaching a Computer or Terminal

The MCU connects to the controlling device via a TTL, non-inverted serial port terminating at a 6-pin header. The header fits the plug of an FTDI USB-to-serial cable, but can also be used with an external FTDI USB-to-serial module. A plain RS-232 connection is possible, but the DFP firmware would have to be recompiled with bit rate low enough to work with RS-232 connections.

The serial parameters are 460,800 bps, 8 data bits, 1 stop bit, no parity, and no software or hardware flow control.

C3.4.2. The Two Consoles of the DFP

The serial connection provides access to two multiplexed terminals.

The DFP Console allows testing and interaction with the virtual front panel, as well as debugging facilities. It lets a human or controlling computer operate the front panel over a serial link. (Virtual Front Panel)

The Virtual Console provides a simple but functional terminal for the CFT computer to use to interact with the user. This is the first user interface device provided by the CFT, followed by the TTY card (two or four RS-232 serial ports) and the VDU card (video output and keyboard input).

The user normally interacts with the DFP Console, but can activate the Virtual Console at will with the cons command. With the virtual console activated, the user is interacting with whatever program is running on the computer. An escape character sequence returns to the DFP Console.

This is similar in spirit to operating a Hayes-style Smart Modem using AT commands, or using a lights-out remote server management system on 21st century server hardware.

C3.4.3. Interacting with the DFP Console

The DFP firmware presents an interactive user interface intended for both humans and machines, in the style of the SMTP, FTP and HTTP protocols. The user enters short commands, optionally followed by one or more arguments, and the board responds with a three digit response code and a human-readable message. A human usually ignores the response code; a machine usually ignores the textual message.

On boot up, the DFP will display a sequence of diagnostic and informational messages like this:

101 Processor: found 201 Version: 1.2 2016-06-10+dis 102 VP Shift Reg chain: OK 103 DEB Shift Reg chain: OK 104 ABUS driver: OK 105 ABUS tristate: OK 106 DBUS driver: OK 107 DBUS tristate: OK 108 Bus quiet during reset: OK 109 AC: OK 110 PC: OK 111 IR: OK 201 Version: 1.2 2016-06-10+dis 202 (c) 2012-2016 Alexios Chouchoulas 202 Licensed under the GNU Public License v.2. 202 http://www.bedroomlan.org/cft 202 All values base 16 unless otherwise noted. 204 BufSize: 200 205 Processor found. [running]> █

The bottom line is a prompt.

A rudimentary line editor is provided:

- Backspace, DEL or Ctrl-H

- delete the last character in the current command.

- Ctrl-C or Ctrl-X

- abort the current command, and may also be used to abort a long-running process.

- Enter, Return, Ctrl-J, or Ctrl-M

- submit the current command for processing.

- Ctrl-N or Ctrl-P

- repeat the last entered command. Due to memory limitations on the DFP controller, the keys must be the very first character received on a new line for this to work.

- Ctrl-T

- toggles terminal mode. When on, terminal directives for colour output are used, and the output generally looks a little nicer. This is better for humans on modern terminals, but not ideal for other computers.

- Ctrl-L

- reprints the prompt and the current command to fix cases where the output may be mangled by serial communication issues.

Help may be obtained by using the ? or help commands, which print out something like this:

[halted] c021> help 201 Available commands: 201 ? -- Show help 201 help -- Show help 201 ver -- Show version 201 buf -- Show size of command buffer 201 term [ BOOL ] -- Get/set terminal bells & whistles. 201 echo [ BOOL ] -- Get/set local echo. 201 mesg [ BOOL ] -- Get/set async messages. 201 s -- Current CFT/DEB status 201 us -- Microcode control state 201 sws -- Show Switch state 201 abus -- Read Address bus 201 dbus -- Read Data bus 201 swtest -- Test switch assembly and OR 201 dfps -- Show DFP state 201 cons -- Virtual console ( # . to exit). 201 lock [ BOOL ] -- Get/set software switch lock. 201 201 reset [ BOOL ] -- Reset (if TRUE, cold boot) 201 start -- Reset & run 201 stop -- Stop 201 halt -- Stop (same as stop, for versatility) 201 run -- Run 201 step [ N ] -- Step to next fetch (default: 1) 201 ustep [ N ] -- Microstep the CPU (default: 1) 201 trace -- Status trace 201 utrace -- Microcode status trace 201 bp [ NUM [ off | ADDR ] ] -- Set breakpoint (see docs) 201 hof [ BOOL ] -- Get/set halt on FAIL 201 hos [ BOOL ] -- Get/set halt on SENTINEL 201 fast -- CPU at full speed 201 slow -- CPU at slow speed 201 creep -- CPU at creep speed 201 clk PS DIV -- Arbitrary clock speed (see docs). 201 201 ir [ WORD ] -- Get/set IR 201 pc [ WORD ] -- Get/set PC 201 ac [ WORD ] -- Get/set AC. 201 201 a [ WORD ] -- Get/set address 201 r -- Read mem[a++] 201 d [ C ] -- Dump C words (default: 80) 201 dis [ C ] -- Disassemble C words (default: 10) 201 db [ C ] -- Binary dump C words (default: 80) 201 w WORD [ WORD... ] -- Write c words to mem[a++] 201 fill COUNT VALUE -- Fill memory 201 in ADDR -- Read I/O address ADDR 201 out ADDR WORD -- Write WORD to I/O addr ADDR. 201 201 i1 -- Signal IRQ1 201 i6 -- Signal IRQ6 201 sr -- Read front panel switches 201 or [ WORD ] -- Get/set OR lights 201 201 Ctrl-C Ignore command line, stop output, abort command. 201 Ctrl-X Ignore command line. 201 Ctrl-T Toggle terminal mode. 201 Consult documentation for more details. [halted] c021> █

The prompt takes two forms. When the computer is running:

[running]> █

When the computer is halted, the prompt changes to display this fact and the current address where data is entered.

[halted] 826c> █

For the benefit of humans, the firmware makes use of colours using a tiny subset of ANSI X3.64 terminal directive. User input is shown in yellow; asynchronous messages are in purple. Flags turned on are in green. Flags turned off are in red. Some important bits of information are displayed in white, or bold. Errors are in red.

C3.4.4. Hardware Diagnostics

When first started up (or when cold reset via the reset y command), the DFP will go through a series of hardware diagnostics to verify its own health, the health of its interface to the CFT hardware, and the CFT hardware itself. During these diagnostics, the DFP Console prints out diagnostic messages, and the OR lights reflect the same information. For a test code like 103, the lights will display 0103 or 0000·0001·0000·0011. The following diagnostics are currently performed:

- 101:

- Processor presence test.

- 102:

- Virtual Front Panel shift chain test. This ensures the virtual front panel inputs are operating properly and shifting data correctly to the microcontroller at the fastest possible rate.

- 103:

- Debugging shift chain test. This ensures the debugging inputs are operating properly and shifting data correctly to the microcontroller at the maximum possible rate.

- 104:

- Address Bus Driver tests. This ensures the DFP can drive the address bus correctly. The test outputs a number of bit patterns to the address bus and ensures they are read back correctly.

- 105:

- Address Bus tri-state tests. This ensures the DFP can release the address bus and let it float correctly.

- 106:

- Data Bus Driver tests. This ensures the DFP can drive the data bus correctly. The test outputs a number of bit patterns to the data bus and ensures they are read back correctly.

- 107:

- Data Bus tri-state tests. This ensures the DFP can release the data bus and let it float correctly.

- 108:

- Bus quiet during reset. Ensures there is no bus traffic while reset is being asserted.

- 109:

- AC tests. Ensures the AC can be written to correctly, and the same values written can be read back.

- 110:

- PC tests. Ensures the PC can be written to correctly, and the same values written can be read back.

- 111:

- IR tests. Ensures the IR can be written to correctly, and the same values written can be read back.

C3.4.5. When Hardware Diagnostics Fail

If any of the DFP diagnostics fail, the DFP freezes, does not allow the computer to start, and blinks the STOP light slowly. Eight seconds later, it performs a cold reset and reruns the diagnostics. This is to account for cases where a diagnostic terminal has been connected halfway through the process.

On failure, the OR will display the code of the test that failed:

- 0101:

- the processor was not found. The DFP firmware was originally coded to run without a processor necessarily present, but this is becoming far less useful as the project goes on and a missing processor is now a fault.

- 0102:

- The Virtual Front Panel shift chain test failed. Bits are not propagating correctly along the chain. The shift registers may be improperly connected, faulty, or incapable of supporting the data rate of the DFP microcontroller. There may be excessive noise in the area.

- 0103:

- The Debugging shift chain test failed. Bits are not propagating correctly along the chain. The shift registers may be improperly connected, faulty, or incapable of supporting the data rate of the DFP microcontroller. There may be excessive noise in the area.

- 0104:

- The DFP was unable to drive the address bus, write values to it, and/or read them back correctly. Mismatches between expected and seen values will be shown on the DFP Console.

- 0105:

- The DFP was unable to tri-state the address bus, the address bus hold circuitry is missing, or is faulty. There may be excessive noise in the area.

- 0106:

- The DFP was unable to drive the data bus, write values to it, and/or read them back correctly. Mismatches between expected and seen values will be shown on the DFP Console.

- 0107:

- The DFP was unable to tri-state the data bus, the address bus hold circuitry is missing, or is faulty. There may be excessive noise in the area.

- 0108:

- Bus chatter was detected during a reset. The processor's reset circuitry may be broken, a peripheral may be misbehaving, or there is excessive noise in the environment. Bus hold circuitry may be malfunctioning.

- 0109:

- The AC is malfunctioning. Values were unable to be written, written incorrectly, read back incorrectly or not read back at all. Value mismatches will be printed out to the DFP Console.

- 0110:

- The PC is malfunctioning. Values were unable to be written, written incorrectly, read back incorrectly or not read back at all. Value mismatches will be printed out to the DFP Console.

- 0111:

- The IR is malfunctioning. Values were unable to be written, written incorrectly, read back incorrectly or not read back at all. Value mismatches will be printed out to the DFP Console.

C3.4.6. Computer Mode

When operated by a computer, it is useful to disable features needed mostly by humans. A hidden ‘computer mode’ is provided for this purpose. Sending ASCII code 30 to the DFP Console enters this mode, disabling echo and terminal mode:

[running]> ***

312 Terminal: off

310 Echo: off

299 T0sgQ09NUFVURVI=

[running]> █To disable computer mode, type (the first line in the blind):

[running]> echo on 310 Echo: on [running]> term on 312 Terminal: on [running]> █

C3.4.7. Asynchronous Messages

The DFP is asynchronous by nature. Whenever switches are operated or the DFP issues an instruction to it, the DFP Console reacts by printing out an appropriate message asynchronously, then repeating the prompt and as much of the input line as the user has entered. This can be annoying when simultaneously entering commands on the DFP Console as it interrupts typing. To mitigate the problem partially in terminal mode, the input line remains at the bottom of the screen and asynchronous messages scroll up from Asynchronous messages are displayed in magenta (with terminal mode activated):

[halted] ff84> start 306 Host reset 304 Host running [running]> 345 SUCCESS [running]> 340 PRINTH 0000 [running]> 340 PRINTH 0000 [running]> 340 PRINTc 10 [running]> 305 Host halted [halted] c021> █

With terminal mode off, the line is interrupted by three asterisks *** and asynchronous messages always start at the beginning of the line to simplify parsing:

[halted] ff84> start

306 Host reset

304 Host running

[running]> ***

345 SUCCESS

[running]> ***

340 PRINTH 0000

[running]> ***

340 PRINTH 0000

[running]> ***

340 PRINTc 10

[running]> ***

305 Host halted

[halted] c021> █Asynchronous messages can be disabled using the mesg n command:

[halted] c021> mesg no 311 Async messages: off [halted] c021> █

C3.4.8. How the DFP Console Reacts to Front Panel Activity

When most of the front panel switches are operated, the DFP logs an appropriate message to the DFP console. This message is often the exact same message shown when the corresponding commands are issued via the DFP console. The only way to distinguish front panel operations from virtual front panel operations is thus the asynchronous nature of the message: if a message about a change to the SR is received, and no change to the SR has been requested, then this is a result of a front-panel operation. During testing, it is beneficial for the panel to be locked to avoid test failures due to this. The automated test framework locks the front panel during testing.

C3.4.8.1. Using the Run Control Switches

Operating these switches will log appropriate messages to the DFP Console. When the STOP switch is actuated:

[running]> 305 Host halted

When the RUN switch is actuated:

[halted] e010> 304 Host running

When the RESET switch is actuated:

[halted] 0182> 306 Host reset

When the START switch is actuated:

[halted] 0182> 306 Host reset [halted] 0182> 304 Host running

When stepping and microstepping, a detailed dump of the computer's state is printed. The STEP switch prints out the PC, AC and IR and disassembles the IR. The µSTEP switch additionally prints out the micro-instruction control vector and decodes that. In the example below, the computer steps through an ISZ instructions, and then micro-steps the last step of fetching the next instruction (a LOAD) and executing that.

[halted] e00d> 323 Step. n---- PC:e00d AC:e000 IR:e000 ISZ &000 [halted] e00d> 324 Microstep. n---- PC:e00e AC:93cf IR:ebbe ISZ I &3be 001100000000000001000000 IR <- mem[ar] [halted] e00e> 324 Microstep. n---- PC:e010 AC:93cf IR:203c LOAD &03c 000000000000000000100010 AR <- AGL [halted] e010> 324 Microstep. n---- PC:e010 AC:93cf IR:203c LOAD &03c 001100000000000001100000 AC <- mem[ar] [halted] e010> 324 Microstep. -z--- PC:e010 AC:0000 IR:203c LOAD &03c 100000000000000000000000 END

Changing the clock speed will issue one of these messages:

[halted] e010> 327 Full speed clock. [halted] e010> 328 Slow clock. [halted] e010> 329 Very slow clock.

C3.4.8.2. The Panel Lock Key Switch

When the panel lock key switch is operated, the panel lock is enabled or disabled, and one of the following messages appear:

[running]> 374 Panel lock: on [running]> 374 Panel lock: off

C3.4.8.3. Changes to the Switch Register

The entire SR is output as an asynchronous message whenever any of its switches are operated. The SR is displayed in hexadecimal, decimal, and as an Assembly instruction (if disassembly is included in this firmware).

[running]> 220 Switch Register: 0000000000000001 0001 1 TRAP &001 [running]> 220 Switch Register: 0000000000000011 0003 3 TRAP &003 [running]> 220 Switch Register: 0000000000000111 0007 7 TRAP &007 [running]> 220 Switch Register: 0000000000001111 000f 15 TRAP &00f [running]> 220 Switch Register: 0000000001001111 004f 79 TRAP &04f [running]> 220 Switch Register: 0000000001101111 006f 111 TRAP &06f [running]> 220 Switch Register: 0010000001101111 206f 8303 LOAD &06f [running]> 220 Switch Register: 0110000001101111 606f 24687 JMP &06f [running]> 220 Switch Register: 0110100001101111 686f 26735 JMP I &06f [running]> 220 Switch Register: 0110110001101111 6c6f 27759 JMP I R &06f

C3.4.8.4. Using the Programming Switches

The effects of some of the programming switches may be slightly counter-intuitive, but show their side effects much more clearly. When the SR→PC, SR→IR and SR→AC switches are operated, obvious messages are logged: (here, the SR is set to e000)

[halted] 0000> 354 PC: e000 [halted] e000> 355 IR: e000 [halted] e000> 353 AC: e000

The examine/deposit switches show their side effects in detail. The only way to distinguish between the plain and NEXT variants (automatic address advance) of the operations is the fact that the address in the prompt steps after each switch operation. For example, the log below starts with three presses of the MEM W NEXT switch, followed by a single press of the MEM W switch (where the e004 address does not increment after the switch press).

[halted] e000> 370 Write mem[e000] <- e000 [halted] e001> 370 Write mem[e001] <- e000 [halted] e002> 370 Write mem[e002] <- e000 [halted] e003> 370 Write mem[e003] <- e000 [halted] e004> 370 Write mem[e004] <- e000 [halted] e004> 371 Read mem[e004] -> 0123 [halted] e005> 371 Read mem[e005] -> ffed [halted] e006> 371 Read mem[e006] -> 76d3 [halted] e007> 371 Read mem[e007] -> ffff [halted] e007> 372 Write I/O[e007] <- e000 [halted] e008> 372 Write I/O[e008] <- e000 [halted] e009> 372 Write I/O[e009] <- e000 [halted] e00a> 372 Write I/O[e00a] <- e000 [halted] e00a> 373 Read I/O[e00a] -> e000 [halted] e00b> 373 Read I/O[e00b] -> e000 [halted] e00c> 373 Read I/O[e00c] -> e000 [halted] e00d> 373 Read I/O[e00d] -> e000

When the RAM/ROM switch changes state, the following is logged:

[halted] e00d> 333 ROM/RAM# switch: RAM [halted] e00d> 333 ROM/RAM# switch: ROM

When the IFR1 and IFR6 switches are operated, the following messages appear.

[halted] e00d> 358 IRQ1 signaled [halted] e00d> 359 IRQ6 signaled

If the CFT has not enabled the IFR1 and/or IFR6 interrupts, the messages are different:

[halted] e00d> 458 IRQ1 masked by CFT [halted] e00d> 459 IRQ6 masked by CFT

C3.4.9. DFP Console Command Reference

C3.4.9.1. ver — Display Version

Displays the current version of the DFP firmware.

[halted] c021> ver 201 Version: 1.2 2016-05-21+dis

C3.4.9.2. buf — Display Buffer Size

Displays the size of the command buffer in hexadecimal. The buffer size dictates the maximum size of a DFP command, and indirectly the speed of automated program entry, since the write to memory (w) command is one of the few that can become very long.

[halted] c021> buf 204 BufSize: 200

C3.4.9.3. term — Get or Set Terminal Mode

The term command shows whether or not terminal mode is enabled, and can enable or disable it. Without an argument, it simply shows the current state:

[halted] c021> term 212 Terminal: on

With an appropriate argument, it controls terminal mode.

[halted] c021> term off 312 Terminal: off [halted] c021> term on 312 Terminal: on

C3.4.9.4. echo — Get or Set Echo

The echo command displays the state of echo, and can also control it. When echo is on, characters sent to the DFP by a terminal are also output back to the terminal. This works well on terminals without local echo (the majority) but is undesirable when a testing computer operates the DFP automatically.

[halted] c021> echo 210 Echo: on [halted] c021> echo off 310 Echo: off [halted] c021> 310 Echo: on

C3.4.9.5. mesg — Get or Set Asynchronous Message Delivery

The mesg command displays and controls the delivery of asynchronous messages. Without an argument, the current state is displayed. With an argument, the state is changed appropriately.

[halted] c021> mesg 211 Async messages: on [halted] c021> mesg yes 311 Async messages: on [halted] c021> mesg no 311 Async messages: off [halted] c021> mesg on 311 Async messages: on [halted] c021> mesg off 311 Async messages: off

C3.4.9.6. s — Get CFT Status

This command shows the current state the CFT processor. Shown are processor flags and the values of the PC, AC and IR. The latter is also disassembled into a symbolic instruction, if disassembly is available.

[halted] c021> s 250 Machine state: -z--l PC:c021 AC:0000 IR:6021 JMP &021

C3.4.9.7. us — Display Microcode Control State

This command reads and displays the current microcode 24-bit control vector in binary form. If disassembly is available, it also decodes it into a human readable string. Please note that this shows the same vector as that displayed on the top row of the front panel, so active-low signals are inverted (‘1’ signifies asserted signals).

[halted] c021> us 252 Microcode control: 000000000000000000100011 AR <- PC

C3.4.9.8. sws — Show Front Panel Switches

Displays, in binary, the current state of all switches on the front panel.

[halted] c021> sws 251 Switch state: 00000000 1001100111100011 001000000000 0000 00000000

Five fields are displayed:

- The state of the left switch group.

- The Switch Register.

- The state of the right switch group.

- The state of the four bit DIP switches.

- The state of the eight bit DIP switches.

The left switches are encoded as follows:

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| SPEED | µSTEP | STEP | RUN | STOP | RESET | LOCK | |

A set bit indicates an activated switch. SPEED encodes the three speeds as follows:

| SPEED | Meaning |

|---|---|

| 10 | Full clock speed. |

| 11 | Slow clock speed. |

| 01 | Creep clock speed. |

| 00 | Should never happen! |

The switch register is displayed in the second field, in the conventional binary form with the most significant to the left. 1 indicates a switch is up or on.

The third field shows the state of the right hand switches.

| 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| IFR1 | IFR6 | ROM | PROG | SR→AC | SR→IR | SR→PC | |||||

A set bit indicates an activated switch. PROG encodes the programming switches. When decoding these switches, the firmware ignores all patterns not listed below. This provides software interlock and prioritisation. If multiple switches are operated simultaneously, the action will be ignored. For example, if both the Memory Deposit and I/O Write Next switches are activated, the pattern would be 01011, and nothing would happen.

| PROG | Meaning |

|---|---|

| 00001 | Memory Deposit switch operated. |

| 00011 | Memory Deposit Next switch operated. |

| 00100 | Memory Examine switch operated. |

| 00101 | Memory Examine Next switch operated. |

| 01000 | I/O Write switch operated. |

| 01001 | I/O Write Next switch operated. |

| 10000 | I/O Read switch operated. |

| 10001 | I/O Read Next switch operated. |

| All others | Should never happen! |

The fourth and fifth fields are simply the state of the 12 DIP switches.

C3.4.9.9. swtest — Test front panel switches

Helps the user perform a test of most switches on the front panel. This command allows all switches to be operated with impunity, with no changes made to the computer. It shows all changes to switch states, using the same output as the sws command.

To test the switches, every change to a switch must log a line on the DFP console, and not changing any switches must not log any lines. Use the sws command reference above to ensure the correct bits are changed.

When done, press Ctrl-C to terminate the command.

[halted] c021> swtest 334 Operate toggles/DIP switches. Ctrl-C ends. 251 Switch state: 00000000 0000000000000000 001000000000 0000 00000000 251 Switch state: 00000000 0000000000000001 001000000000 0000 00000000 251 Switch state: 00000000 0000000000000011 001000000000 0000 00000000 251 Switch state: 00000000 0000000000000111 001000000000 0000 00000000 251 Switch state: 00000000 0001000000000111 001000000000 0000 00000000 251 Switch state: 00000000 0011000000000111 001000000000 0000 00000000 251 Switch state: 00000000 0111000000000111 001000000000 0000 00000000 251 Switch state: 00000000 1111000000000111 001000000000 0000 00000000 251 Switch state: 00000000 0111000000000111 001000000000 0000 00000000 251 Switch state: 00000000 0011000000000111 001000000000 0000 00000000 301 Done [halted] c021> █

C3.4.9.10. abus — Read the Address Bus

This command reads the current value of the Address Bus and prints it out. The computer must be halted. Both CFT and DFP drive the Address Bus only when performing memory cycles, so the value read will either be the value currently being driven, or the last value written (since the CFT has bus hold circuitry).

[halted] c021> abus 260 ABUS: c021

C3.4.9.11. dbus — Read the Data Bus

This command reads the current value of the Data Bus and prints it out. The computer must be halted. Since the Data Bus is only driven part of the time, the value read here may be the last value read from the Data Bus (a result of bus hold circuitry), and not a current value. There is no way to determine whether a circuit is driving the Data Bus.

[halted] c021> dbus 261 DBUS: 0000

C3.4.9.12. dfps — Show DFP State

[halted] c021> dfps 201 Version: 1.2 2016-05-21+dis 204 BufSize: 200 205 Processor found. 212 Terminal: on 210 Echo: on 211 Async messages: off 215 Front panel lock: off 213 On FAIL: off 214 On SENTINEL: off 203 Address: c021 221 Output Register: 0000 220 Switch Register: 0011000000000111 3007 12295 STORE &007 260 ABUS: c021 261 DBUS: 0000 251 Switch state: 00000000 0011000000000111 001000000000 0000 00000000 [halted] c021> █

C3.4.9.13. cons — Enter Virtual Console

This command switches from the DFP Console to the CFT Virtual Console, an emulated serial port that allows the computer to be interacted with before a serial board is built for it. To escape back from the Virtual Console to the DFP Console, press Enter followed by #..

[running]> cons 331 Virtual console (press Enter # . to exit). ... interacting with the CFT ... #. 332 Left virtual console. [running]> █

An improvement

Thecons command needs an optional argument that starts the console and sets the computer running at the same time. This is useful for testing, and an easy way to perform a common task. It should also issue a warning if the computer is halted and the console is started without this argument (but start the console anyway—the operator might want to use the front panel switches instead).A necessary fix

When the DFP Console is active, characters written to the CFT Virtual Console are reported as asynchronous messages. This should probably not happen. To fix it, the dfp.TX I/O address must be made separate from the PRINTC one, and the part of the Firmware that handles dfp.TX needs to change to handle this special case.C3.4.9.14. lock — Panel Lock

This command sets or clears the panel lock, overriding the state of the physical switch. The physical switch can, in turn, override this one if operated. With the lock activated, only the SRand IFR switches are operable. All others are locked out. The logical lock is useful (among other things) for locking the front panel out while running sensitive tests on the processor.

[halted] c021> lock 215 Front panel lock: off [halted] c021> lock on 315 Front panel lock: on [halted] c021> lock off 315 Front panel lock: off [halted] c021> █

C3.4.9.15. reset — Reset the computer

This command resets the computer. If the computer is running, it will immediately start executing at address FFF8. If the computer is halted, it will simply perform a reset. This will also reset any peripherals on the bus that act on the

[halted] c021> reset 306 Host reset

Another function of the reset command is to carry out a cold reset of the DFP. This will revert the DFP to its power-on state. It will also reset the processor and all peripherals, and go through all DFP diagnostics. To perform a cold reset, execute reset cold.

0 or no, noor off.200 Ready [halted] c021> reset cold 307 Cold reset 101 Processor: found 201 Version: 1.2 2016-06-10+dis 102 VP Shift Reg chain: OK 103 DEB Shift Reg chain: OK 104 ABUS driver: OK 105 ABUS tristate: OK 106 DBUS driver: OK 107 DBUS tristate: OK 108 Bus quiet during reset: OK 109 AC: OK 110 PC: OK 111 IR: OK 201 Version: 1.2 2016-06-10+dis 202 (c) 2012-2016 Alexios Chouchoulas 202 Licensed under the GNU Public License v.2. 202 http://www.bedroomlan.org/cft 202 All values base 16 unless otherwise noted. 204 BufSize: 200 205 Processor found. [running]> █

C3.4.9.16. start — Start the computer

This command resets the computer and starts its clock. The processor will immediately start executing at address FFF8. Any peripherals on the bus that act on the

[halted] 826d> start 306 Host reset 304 Host running

C3.4.9.17. stop or halt — Stop the computer

This command waits until the computer has completed its current instruction, then halts the clock. The exact microstep when the clock is stopped is configurable, but is usually set to the last step of the Fetch state.

[running]> halt 305 Host halted

C3.4.9.18. run — Continue Execution

This command re-enables the clock and resumes execution.

[halted] e348> start [running]> halt 305 Host halted 304 Host running

C3.4.9.19. step — Single-stepping

With the computer halted, this instruction will single-step once and print out the computer's state. An optional hexadecimal number can be provided to perform multiple single steps.

Multiple microsteps can be aborted using Ctrl-C, operating the STOP switch on the front panel, or if an extended instruction halts the processor (this includes HALT and FAIL when Halt-on-Fail is enabled).

[running]> step 503 Halt host first [running]> halt 305 Host halted [halted] 826c> step 5 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 301 Done [halted] 826c> step 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c [halted] 826c> step 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c [halted] 826c> run 304 Host running

Tip

When single-stepping, pressing Ctrl-N re-runs the previous command and saves typing the wholestep command anew.Tip

A long sequence of steps can always be stopped early using Ctrl-C.C3.4.9.20. ustep — Microstepping

This command works much like the step command, but it performs microsteps instead. The output of each step includes the computer's state plus the microcode control vector in binary and symbolic form.

Multiple microsteps can be aborted using Ctrl-C, operating the STOP switch on the front panel, or if an extended instruction halts the processor (this includes HALT and FAIL when Halt-on-Fail is enabled).

[running]> ustep 5 503 Halt host first [running]> halt 305 Host halted [halted] 826c> ustep 5 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC 301 Done [halted] 826c> ustep 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC [halted] 826c> ustep 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC [halted] 826c> run 304 Host running

Tip

A long sequence of steps can always be stopped early using Ctrl-C.todo

The strange behaviour of the example above is due to a microstepping bug in the emulated DFP. Microstepping normally steps through instructions, and doesn't repeat the same microinstruction endlessly.C3.4.9.21. trace — Trace code execution

The trace command simply runs the step command continuously. The endless sequence of steps can be aborted using Ctrl-C or operating the STOP switch on the front panel. It will also stop if an extended instruction halts the processor (this includes HALT and FAIL when Halt-on-Fail is enabled). It will also stop if a breakpoint is encountered.

[halted] 826c> trace 325 Tracing. 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 323 Step. ----- PC:826c AC:0000 IR:626c JMP &26c 302 Aborted

Yes, yes, I know it's a bad example

JMP to the current address, so the PC will never change anyway. I'm not sure why I collected this particular example. I'll eventually get a better one.C3.4.9.22. utrace — Trace microcode execution

The utrace command simply runs the ustep command continuously. The endless sequence of micro-steps can be aborted using Ctrl-C or operating the STOP switch on the front panel. It will also stop if an extended instruction halts the processor (this includes HALT and FAIL when Halt-on-Fail is enabled), or if a breakpoint is encountered.

[halted] 826c> utrace 326 Microtracing. 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC 324 Microstep. ----- PC:826c AC:0000 IR:626c JMP &26c 000000000000000000100011 AR <- PC 302 Aborted [halted] 826c> █

To Do

The strange behaviour of the example above is due to a microstepping bug in the emulated DFP. Microstepping normally steps through instructions, and doesn't repeat the same microinstruction endlessly.C3.4.9.23. bp — Breakpoint Facility

step, ustep, trace and utrace commands. When the computer runs normally, breakpoints will not be honoured.The DFP supports up to eight breakpoints. These can be either off, or set to any 16-bit address, which implies that they are somewhat limited if the MBU is installed, enabled and memory banks switch.

To list breakpoints, issue the bp command without any arguments.

[halted] 826c> bp 259 Breakpoint 0: off 259 Breakpoint 1: off 259 Breakpoint 2: off 259 Breakpoint 3: off 259 Breakpoint 4: off 259 Breakpoint 5: off 259 Breakpoint 6: off 259 Breakpoint 7: off

To set a breakpoint, use the bp command with two arguments: a breakpoint number in the range 0–7 and a hexadecimal address.

[halted] 826c> bp 0 c000 259 Breakpoint 0: c000 [halted] 826c> bp 1 c500 259 Breakpoint 1: c500

To examine specific breakpoints, use a single argument denoting the breakpoint number.

[halted] 826c> bp 0 259 Breakpoint 0: c000 [halted] 826c> bp 2 259 Breakpoint 2: off

To disable a breakpoint, use off as its address:

[halted] 826c> bp 0 c000 259 Breakpoint 0: c000 [halted] 826c> bp 0 off 259 Breakpoint 0: off [halted] 826c> bp 259 Breakpoint 0: off 259 Breakpoint 1: c500 259 Breakpoint 2: off 259 Breakpoint 3: off 259 Breakpoint 4: off 259 Breakpoint 5: off 259 Breakpoint 6: off 259 Breakpoint 7: off

To Do

Showtrace or step execution with breakpoints set.C3.4.9.24. hof — Halt on FAIL

This command inspects or sets the Halt-on-Fail setting. When Halt-on-Fail is on, executing a FAIL instruction will also halt the computer. A suitable failure message is always printed on the DFP and Virtual Consoles regardless of the state of this setting. The setting may also be modified programmatically using the ENEF or DISEF extended instructions.

[running]> hof 213 On FAIL: off [running]> hof on 313 On FAIL: on [running]> hof off 313 On FAIL: off [running]> █

C3.4.9.25. hos — Halt on SENTINEL

This command inspects or sets the Halt-on-Sentinel setting. When Halt-on-Sentinel is on, executing a SENTINEL instruction will also halt the computer. A suitable message is always printed on the DFP and Virtual Consoles regardless of the state of this setting. The setting may also be modified programmatically using the ENEF or DISEF extended instructions.

[running]> hos 214 On SENTINEL: off [running]> hos on 314 On SENTINEL: on [running]> hos off 314 On SENTINEL: off [running]> █

C3.4.9.26. fast — Full Clock Speed

This command disables the DFP's clock generator and enables the processor's. The processor will operate at its full speed. The setting of the speed switch on the front panel will be overridden until the switch is operated again.

[running]> fast 327 Full speed clock. [running]> █

C3.4.9.27. slow — Slow Clock Speed

This command disables the processor's clock generator and enables the DFP's. The DFP will direct the processor using a slow clock, which allows instruction execution to be seen on the front panel. The setting of the speed switch on the front panel will be overridden until the switch is operated again.

[running]> slow 328 Slow clock. [running]> █

C3.4.9.28. creep — Very Slow Clock Speed

This command disables the processor's clock generator and enables the DFP's. The DFP will direct the processor using a very slow clock, which allows micro-instruction execution to be seen on the front panel (also instruction execution, if one is inhumanly patient, drugged up, or an Ent). The setting of the speed switch on the front panel will be overridden until the switch is operated again.

[running]> creep 329 Very slow clock. [running]> █

What the Hell am I Doing Here?

Should I change message329 to 329 Weirdo? I think I should. C3.4.9.29. clk — Custom Clock Speed

This command disables the processor's clock generator and enables the DFP's using a custom clock rate. The setting of the speed switch on the front panel will be overridden until the switch is operated again.

The clock rate is specified in the form of two parameters: a prescaler 1 ≤ psn ≤ 5, and a 16-bit divisor 0 ≤ div ≤ 65535 (specified, as always, in hexadecimal). These directly drive the MCU's pulse-width modulator, generating a frequency of:

The psn parameter selects the prescaler value like this:

psn | Prescaler |

|---|---|

| 1 | 2 |

| 2 | 16 |

| 3 | 128 |

| 4 | 512 |

| 5 | 2,048 |

[running]> clk 1 2 330 Clock set to 14745600 Hz / (2 * (1 + 2)) (base 10) [running]> clk 1 123 330 Clock set to 14745600 Hz / (2 * (1 + 291)) (base 10) [running]> clk 2 124 330 Clock set to 14745600 Hz / (16 * (1 + 292)) (base 10) [running]> clk 3 200 330 Clock set to 14745600 Hz / (128 * (1 + 512)) (base 10) [running]> clk 4 42 330 Clock set to 14745600 Hz / (512 * (1 + 66)) (base 10) [running]> clk 1 100 330 Clock set to 14745600 Hz / (2 * (1 + 256)) (base 10) [running]> clk 2 9 330 Clock set to 14745600 Hz / (16 * (1 + 9)) (base 10) [running]> clk 3 a 330 Clock set to 14745600 Hz / (128 * (1 + 10)) (base 10) [running]> clk 4 b 330 Clock set to 14745600 Hz / (512 * (1 + 11)) (base 10)i [running]> clk 5 c 330 Clock set to 14745600 Hz / (2048 * (1 + 12)) (base 10) [running]> █

Please be aware that it is possible to generate exceedingly slow clocks with this command: the slowest clock is just over 0.1 Hz, where it takes 10 seconds for a single clock tick. The processor's clock generator divides this by 4, so a single micro-instruction will step in 40 seconds. The clock will be used when the computer is running, but also when it is stepping or microstepping, and it also affects the length of time it takes for the computer to stop when the STOP switch is operated on the front panel. If a very slow clock is requested (approximately 0.22 Hz here), the DFP will issue a warning:

[running]> clk 5 8000 430 Warning: stopping/stepping will be REALLY slow. 330 Clock set to 14745600 Hz / (2048 * (1 + 32768)) (base 10) [running]> █

C3.4.9.30. ir — Get or Set the Instruction Register

This command displays or changes the current value of the IR. This can only be done with the host halted.

[running]> ir 255 IR: 0000 [running]> ir 1234 503 Halt host first [running]> halt 305 Host halted [halted] 826c> ir 1234 355 IR: 1234 [halted] 826c> ir 255 IR: 1234 [halted] 826c> █

Note that register changes are always verified by the DFP to detect faulty hardware or cases where, during microprogram debugging, the control vector is overriding that particular action. An appropriate error is output in such a case:

[halted] 826c> ir 255 IR: 626c [halted] 826c> ir 1234 355 IR: 626c 910 Value mismatch. Wrote 1234, was 626c [halted] 826c> █

C3.4.9.31. pc — Get or Set the Program Counter

This command displays or changes the current value of the PC. This can only be done with the host halted.

[running]> pc 1234 503 Halt host first [running]> halt 305 Host halted [halted] 826c> pc fff8 354 PC: fff8 [halted] 826c> pc 254 PC: fff8 [halted] 826c> █

C3.4.9.32. ac — Get or Set the Accumulator

This command displays or changes the current value of the AC. This can only be done with the host halted.

[running]> ac 1234 503 Halt host first [running]> halt 305 Host halted [halted] 826c> ac 4342 353 AC: 4342 [halted] 826c> ac 253 AC: 4342 [halted] 826c> █

C3.4.9.33. a — Set the Address

This command shows or sets the current address. This address is used by a number of other panel operations.

[halted] 826d> a 203 Address: 826d [halted] 826d> a 2000 203 Address: 2000 [halted] 2000> pc 254 PC: 826d [halted] 2000> █

Please note that this will not modify the PC. The only way for the physical front panel to set an address is to change the PC to it, while the virtual front panel has a separate address to ease debugging without having to constantly restore the value of the PC.

C3.4.9.34. r — Examine memory

This command reads and prints out consecutive words from the current memory address, which may be set at any point with the a command. The address is incremented every time the instruction is issued. The host must be halted.

[running]> r 503 Halt host first [running]> halt 305 Host halted [halted] 826d> a 2000 203 Address: 2000 [halted] 2000> r 356 Read: 8264 [halted] 2001> r 356 Read: e023 [halted] 2002> r 356 Read: 0000 [halted] 2003> █

C3.4.9.35. d — Hex Dump Memory

This command prints a CFT-style hexadecimal dump of memory starting at the current address, which may be set at any point with the a command. An optional hexadecimal argument may be used to dump a specified number of words. The default is 80, which dumps 128 words. The d command always dumps in groups of 8 words. If the optional argument is not a multiple of 8, it is rounded up.

[halted] 826d> a 8480 203 Address: 8480 [halted] 8480> d 8480: 646f 3a65 2020 0000 4d0a 6d65 726f 3a79 ........ ode: ...Memory: 0002264b 8488: 2020 2020 2020 0000 4b20 2057 4152 2c4d ........ .. KW RAM, 00035fc1 8490: 0020 4b20 2057 4f52 0a4d 0000 6544 6574 ....... . KW ROM...Dete 0004efaf 8498: 7463 6465 203a 2020 0020 6554 6d72 6e69 .... ... cted: .Termin 00074a20 84a0: 6c61 3a73 2020 0020 424d 0055 4644 0050 ... .U.P als: .MBU.DFP. 00089a6a 84a8: 5249 0043 5454 0059 4449 0045 5452 0043 .C.Y.E.C IRC.TTY.IDE.RTC. 0009dac6 84b0: 4d54 0052 564e 0052 4446 0043 5053 004a .R.R.C.J TMR.NVR.FDC.SPJ. 000b1432 84b8: 5350 0047 504c 0054 4456 0055 5445 0048 .G.T.U.H PSG.LPT.VDU.ETH. 000c51a1 84c0: 4947 004f 3f3f 003f 6e45 6976 6f72 6d6e .O.?.... GIO.???.Environm 000e8f50 84c8: 6e65 3a74 0020 6576 6972 6f6c 0a67 0000 .. ..... ent: .verilog... 00108104 84d0: 736a 652d 756d 0000 6d65 6c75 7461 726f ........ js-emu..emulator 00138fb2 84d8: 000a 3432 2400 3cb5 f52a 3431 f132 3430 ........ ..24.$5<*u142q04 00167360 84e0: 60e9 3432 2400 3cb5 f547 3431 f153 3430 ........ i`24.$5<Gu14Sq04 0019b82b 84e8: 60e9 f400 3529 2c31 b5a3 d014 60f4 e431 ........ i`.t)51,#5.Pt`1d 001e394a 84f0: b430 d014 60fe 60eb 2432 3c31 f532 3433 ........ 04.P~`k`2$1<2u34 0022093f 84f8: 2c31 3434 0da6 dcb5 3400 6c00 f41e 3529 ........ 1,44&.5\.4.l.t)5 00251d46 301 Done [halted] 8500> d 1 8500: dcb5 3400 0a0a 0a0a 2020 2020 2323 2323 ........ 5\.4.... #### 0001ab4f 301 Done [halted] 8508> d 8 8508: 2323 2323 2e23 2020 2020 2020 232c 2323 ........ #####. ,### 00011b18 301 Done [halted] 8510> d 20 8510: 2323 2323 2323 2323 2323 2323 0a23 2020 ........ #############. 0000fd15 8518: 2323 2323 2323 2323 2323 2323 2c23 2020 ........ #############, 00021c2a 8520: 2320 2020 2020 2020 2020 2020 2020 2020 ........ # 0003202a 8528: 2020 0a23 2320 2323 2323 2027 2020 2327 ........ #. #####' '# 00041741 301 Done [halted] 8530> █

The output is in five groups:

- Address:

- the leftmost column shows the starting address for the row.

- Hexadecimal data:

- the next eight columns are hexadecimal data starting at the row address.

- Word-aligned characters:

- this group decodes word-aligned or unpacked characters, interpreted as ASCII. Characters outside the range 32–126 (inclusive) are shown as dots.

- Byte-aligned characters:

- this group decodes byte-aligned or packed 7-bit ASCII characters. Characters outside the range 32–126 (inclusive) are shown as dots. The eighth bit is ignored, so negative-terminated packed strings (where the eighth bit of each character is used as a string terminator) are still printable.

- Checksum:

- a naïve 32-bit checksum of all data dumped so far (starting with the execution of the

dcommand) in hexadecimal.

C3.4.9.36. dis — Disassemble Program

This command disassembles CFT assembly starting at the current address. An optional hexadecimal number may be provided to disassemble a specific number of words. The default value is 10(16 words).

[halted] 2005> a fff8 203 Address: fff8 [halted] fff8> dis 8 fff8: JMP I &3f9 ; [&fff9] &6bf9 fff9: ISZ I &000 ; [&fc00] &e800 fffa: JMP I R &002 ; [&fc02] &6c02 fffb: TRAP &000 ; [&fc00] &0000 fffc: TRAP &000 ; [&fc00] &0000 fffd: TRAP &000 ; [&fc00] &0000 fffe: TRAP &000 ; [&fc00] &0000 ffff: TRAP &000 ; [&fc00] &0000 301 Done

The disassembly is (by necessity) trivial, but does provide a decoded target address (in brackets) for local page addressing instructions (those without the R bit set). For instance, the JMP I

&3f9 instruction above addresses memory at FFF9.

C3.4.9.37. db — Dump Binary Data