B3.1. Introduction

The CFT design incorporates two separate buses:

- The Control Bus

- provides a local interconnect for signals local to the processor part of the computer. This includes the Internal Bus (IBUS), signals from the Control Unit, and Microcode Store, as well as signals to and from the Arithmetic and Logic Unit (ALU), registers, interrupt controller boards, and all other processor units. This bus connects the four Processor Boards (and, newly, the Debugging Front Panel (DFP)), but may be used future processor extensions. Physically, this bus is implemented using two 40-pin headers, although additional pins are required for some local functions.

- The Expansion Bus

- is meant for 96-pin DIN 41612 ‘Bauform C’ connectors and 100x160mm (3U) Eurocards (IEEE 1101) connected via a 19-slot backplane. It mainly provides a computer-level expansion interface, although many processor extensions can also be attached here. The Expansion Bus allows devices to connect to the memory space, I/O space, and expanded memory space by using the Address Bus, Data Bus, their associated control lines, as well as interrupt lines.

The two buses are not directly connected, but the processor boards bridge some of their signals where and when it is appropriate.

B3.2. The Backplane

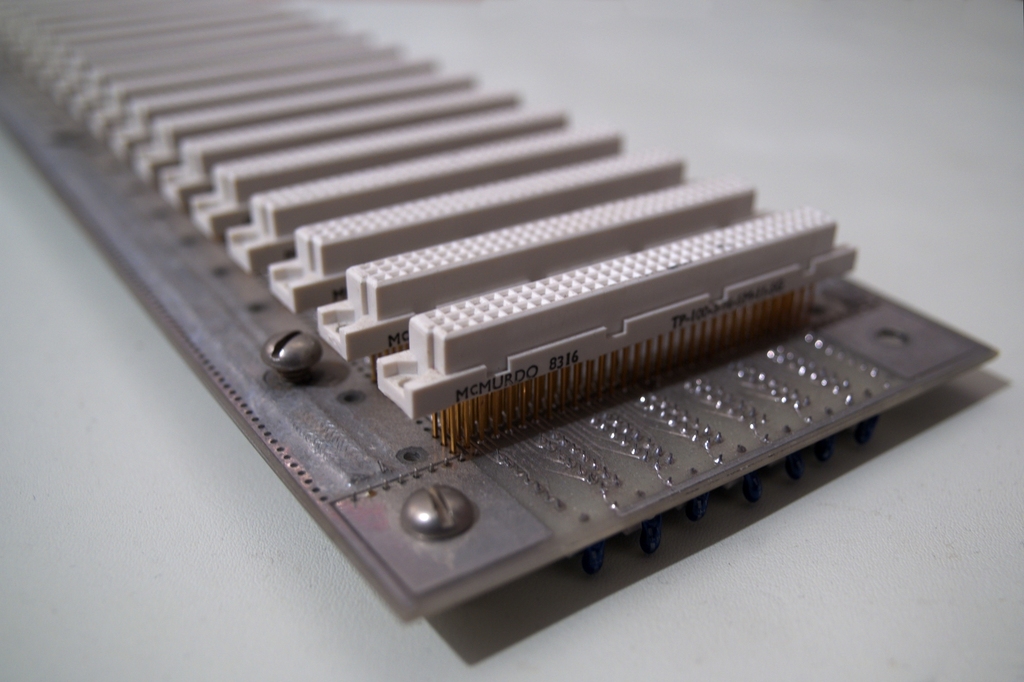

The CFT backplane, shown in is based on a part I've had since late 1993 or early 1994. Historically, it belonged to a computer used and possibly designed at the University of Edinburgh’s Department of Computer Science. The machines were decommissioned circa 1993 and were based on a Motorola MC68020 microprocessor. Despite the Motorola CPU and using DIN 41612, the backplane wasn't VME compatible.

A close-up photo of the backplane, showing around half of its 96-pin DIN 41612 sockets, screws for attaching power terminals, and the pads of the termination resistors (located on the underside of the board). Seven bypass capacitors are visible along the short edge.

The backplane itself is a Eurocard (IEEE 1101) design using DIN 41612 connectors. The connectors are Bauform (style) ‘C’ 96-pin receptacles, the 3×32 pin layout. Here's a diagram of one of the connectors:

A card receptacle on the CFT backplane (as seen from the top) showing the power and ground rails including one reserved for future expansion (which has now been allocated to the 3.3V rail), as well as the two local test point pins. All other pins are connected across the backplane and terminated at either end.

The backplane has five big fat power rails along both long edges. They occupy six entire pin rows (18 pins in total). Of the remaining 78 pins, two pins per connector are not bussed. Instead, they are broken out to test points on the backplane. This leaves 76 pins for bus signals.

All 76 signal pins were terminated at both ends of the bus using a TTL termination scheme. Termination resistors tie each signal to both power and ground rails with an unbalanced pair of resistors, to aid weak TTL drivers and to square signals, as well as to deal with transmission line problems. The termination scheme looked like this:

The original TTL bus termination of the backplane. Obviously meant for TTL drivers.

The resistors clearly form a voltage divider:

The termination helps weak TTL drivers source or sink current to keep waveforms square and reduces transmission line effects. It's a horrible termination scheme for CMOS drivers, though. After a test run that released the precious magic smokefrom a number of components, I pulled the termination resistors and incorporated bus conditioning and termination on the processor boards instead. The backplane itself is unterminated right now. It will stay that way until I see serious issues with the active termination scheme I'm currently using.

B3.3. The Control Bus

The Control Bus is implemented as two separate 40-pin connectors, the 2.54 mm 2×20 pin versions. The connectors are usually marked P1 and P2 and physically reside along the top edge of processor cards, or the rear edge with the backplane horizontal (which is its indented orientation).

The Control Bus provides an interconnect for signals local to the processor part of the computer. Anything peripherals don't need to use (or shouldn't be using!) is on the Control Bus. This includes the IBUS, signals from the Control Unit and Microcode ROMs, as well as signals to and from the ALU, register boards, and all other processor components.

The Control Bus is implemented as a pair of 2×20-pin 2.54 mm headers, identical to the ones used for parallel IDE devices. This makes it cheaper to source cable and plugs, since like most people likely to be reading this, I have more parallel IDE cables lying around than I know what to do with. Two 40-conductor flat cables connect all the cards using the control bus in a daisy-chain fashion. The two pin headers are referred to as P1 and P2, with pins designated P1.1–P1.40 and P2.1–P2.40. Due to renumbering SNAFUs, some processor boards number these as P2 and P3, but they're immediately identifiable by their location on the board anyway.

Even though this is a processor-local bus, trace length is probably long enough for transmission line effects, so all output signals are conditioned using either impedance-matching resistors in series or bus hold circuitry.

There are some signals that normally belong to the Control Bus, but have been relegated to the Expansion Bus because of lack of available pins. Luckily enough, these are signals that processor extension boards can benefit from.

| Pin | Signal | Pin | Signal | Pin | Signal | Pin | Signal |

|---|---|---|---|---|---|---|---|

| P1.1 | CLL | P1.2 | CPL | P1.1 | STPAC | P1.2 | STPDR |

| P1.3 | RAGL | P1.4 | WALU | P1.3 | INCPC | P1.4 | RAC |

| P1.5 | FL | P1.6 | FV | P1.5 | RDR | P1.6 | RPC |

| P1.7 | IR0 | P1.8 | WEN | P1.7 | WAC | P1.8 | WAR |

| P1.9 | IR2 | P1.10 | END | P1.9 | WDR | P1.10 | WPC |

| P1.11 | RUNIT0 | P1.12 | RUNIT1 | P1.11 | FNEG | P1.12 | FZERO |

| P1.13 | RUNIT2 | P1.14 | RUNIT3 | P1.13 | PC10 | P1.14 | PC11 |

| P1.15 | SKIP | P1.16 | STI | P1.15 | PC12 | P1.16 | PC13 |

| P1.17 | CLI | P1.18 | OPIF0 | P1.17 | PC14 | P1.18 | PC15 |

| P1.19 | OPIF1 | P1.20 | OPIF2 | P1.19 | WIR | P1.20 | AINDEX |

| P1.21 | OPIF3 | P1.22 | IR11 | P1.21 | IBUS0 | P1.22 | IBUS1 |

| P1.23 | AC0 | P1.24 | AC1 | P1.23 | IBUS2 | P1.24 | IBUS3 |

| P1.25 | AC2 | P1.26 | AC3 | P1.25 | IBUS4 | P1.26 | IBUS5 |

| P1.27 | AC4 | P1.28 | AC5 | P1.27 | IBUS6 | P1.28 | IBUS7 |

| P1.29 | AC6 | P1.30 | AC7 | P1.29 | IBUS8 | P1.30 | IBUS9 |

| P1.31 | AC8 | P1.32 | AC9 | P1.31 | IBUS10 | P1.32 | IBUS11 |

| P1.33 | AC10 | P1.34 | AC11 | P1.33 | IBUS12 | P1.34 | IBUS13 |

| P1.35 | AC12 | P1.36 | AC13 | P1.35 | IBUS14 | P1.36 | IBUS15 |

| P1.37 | AC14 | P1.38 | AC15 | P1.37 | IR12 | P1.38 | IR13 |

| P1.39 | ACCPL | P1.40 | DEC | P1.39 | IR14 | P1.40 | IR15 |

Here's a description of the control bus signals. For more detailed information, please follow the links to the processor theoretical description.

- CLL (P1.1)

- Output from the Microcode Store, a low level of this signal clears the Link Register (L) asynchronously.

- CPL (P1.2)

- Output from the Microcode Store. Toggles the L.

- FL (P1.5)

- The current value of the L. This is used as input in the Skip and Branch unit, among other places.

- FV (P1.6)

- Output from the ALU. The current state of the Overflow Flag. This flag is used as input in the Skip and Branch unit to aid in signed arithmetic.

- IR0, IR2 (P1.7, P1.9)

- The current value of bits 0 and 2 of the Instruction Register (IR). These are used in the ALU to decode the four roll instructions. Note that the IR is only partially available on the Control Bus. I was out of pins and they weren't needed.

- WEN (P1.8)

- Output by the Microcode Store. When this active low signal is asserted, W (on the Expansion Bus) will be strobed near the end of a memory cycle to signal a write to I/O space or memory.

- END (P1.10)

- Output by the Microcode Store. This active low signal marks the end of a micro-program

- RUNIT0–3 (P1.11–P1.14)

- Output by the Microcode Store. Encodes the vertically-encoded Read Unit number. This is decoded by the Read Unit Decoder and ALU. Some of the decoded values (RAGL, RAC, RDR, and RPC) are output as signals on the Control Bus for the benefit of various processor units. Others (R6 and R7) are on the Expansion bus for future expansion. The remainder are decoded and used locally by the ALU.

- SKIP (P1.15)

- Output by the Skip and Branch Logic (SBL). When asserted, it signals the Microcode Store that a skip or branch must be performed.

- STI (P1.16)

- Output by the Microcode Store. When asserted, it sets the Interrupt Flag (I), allowing subsequent interrupt requests to reach the processor.

- CLI (P1.17)

- Output by the Microcode Store. When low, this signal clears the I, disabling subsequent interrupts.

- OPIF0–3 (P1.18–P1.21)

- Output from the Microcode Store, this four-bit value instructs the SBL to evaluate one of up to 15 conditionals and feed back the output to the SKIP signal.

- IR11–15 (P1.22 and P2.37–P2.40)

- The currently executing micro-program as selected by the IR. These signals are output from the Microcode Store (which houses the IR).

- AC0–15 (P1.23–P1–38)

- Output by the register board providing the full 16-bit value of the Accumulator (AC) register. This is used by the ALU.

- ACCPL (P1.39)

- Output by the register board to toggle the The L Register when incrementing or decrementing the AC causes it to wrap-around.

- DEC (P1.40)

- Output by the Microcode Store to the Register Board. When asserted, it indicates that STPAC and STPDR decrement the AC and Data Register (DR) respectively. When deasserted, the same signals step their registers up.

- STPAC (P2.1)

- Output by the Microcode Store. Steps (increments or decrements) the AC in the direction indicated by DEC.

- STPDR (P2.2)

- Output by the Microcode Store. Steps (increments or decrements) the DR in the direction indicated by DEC.

- INCPC (P2.3)

- Output by the Microcode Store. Increments the Program Counter (PC).

- FNEG (P2.11)

- Output representing the current state of the FNEG. There is no reason for having this signal. I could have just used AB15 for this, since the two are always identical. But I wasn't sure I was going to go that way when I first designed the Control Bus.

- FZERO (P2.12)

- Output by the register board. Contains the current state of the Zero Flag.

- PC10–15 (P2.13–P2.18)

- Output by the register board. The top six bits of PC. These are used by the Address Generation Logic (AGL) to generate page-local addresses.

- AINDEX (P2.20)

- Output from the Auto-Index Unit for the benefit of the Microcode Store. When this active low is asserted, an auto-index micro-program should be executed instead of the indirect micro-program.

- IBUS0–15 (P2.21–P2.36)

- Tri-state bus. The processor’s internal bus, used to exchange values between machine registers and to communicate with the outside world. This bus should only be driven by the currently selected output unit.

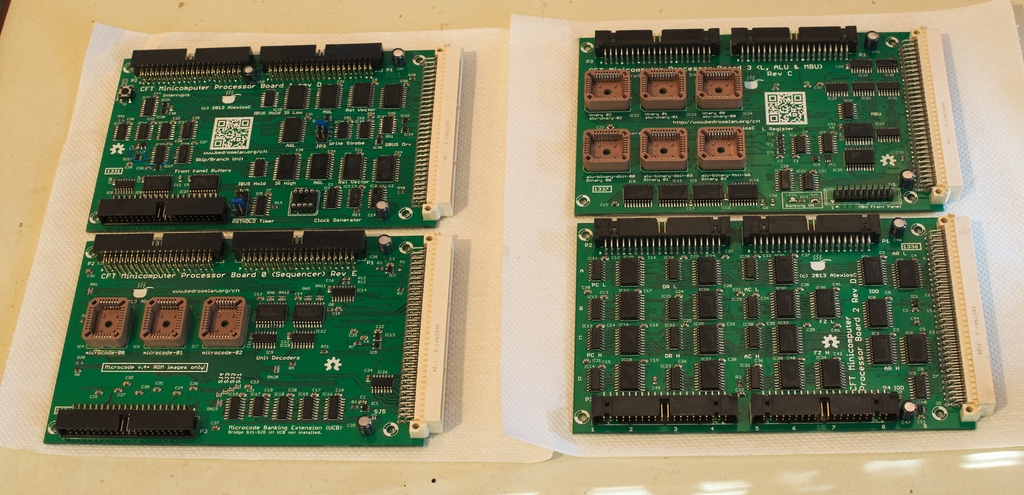

All four Processor Boards showing their twin Control Bus connectors along the top. They also connect to the Expansion Bus for power and signalling using the white DIN 41612 connectors on the right edge of the board. Connectors along the bottom carry signals for the front panel.

B3.4. The Expansion Bus

On most computers with a monolithic, single-chip processor, the processor is self-contained and its internals are cut-off from peripherals. On older computers, the distinction between the processor and its peripherals was nearly non-existent, and their buses reflected this.

The CFT does something like this, or would if there were enough pins on the backplane. However, processor boards do plug into the exact same backplane as normal peripherals and on the same bus. Some peripherals are indistinguishable from processor boards, anyway.

The pin-out of the Expansion Bus is as follows:

| Pin | Signal | Pin | Signal | Pin | Signal |

|---|---|---|---|---|---|

| A.1 | GND | B.1 | GND | C.1 | GND |

| A.2 | GND | B.2 | GND | C.2 | GND |

| A.3 | Vcc (+5V) | B.3 | Vcc (+5V) | C.3 | Vcc (+5V) |

| A.4 | +3.3V | B.4 | +3.3V | C.4 | +3.3V |

| A.5 | AB0 | B.5 | Reserved | C.5 | DB0 |

| A.6 | AB1 | B.6 | SKIPEXT | C.6 | DB1 |

| A.7 | AB2 | B.7 | ENDEXT | C.7 | DB2 |

| A.8 | AB3 | B.8 | WS | C.8 | DB3 |

| A.9 | AB4 | B.9 | R1 | C.9 | DB4 |

| A.10 | AB5 | B.10 | R6 | C.10 | DB5 |

| A.11 | AB6 | B.11 | R7 | C.11 | DB6 |

| A.12 | AB7 | B.12 | W1 | C.12 | DB7 |

| A.13 | IRQ3 | B.13 | AEXT0 | C.13 | MEM |

| A.14 | IRQ4 | B.14 | AEXT1 | C.14 | IO |

| A.15 | IRQ5 | B.15 | AEXT2 | C.15 | R |

| A.16 | IRQ6 | B.16 | AEXT3 | C.16 | W |

| A.17 | TPA | B.17 | AEXT4 | C.17 | TPC |

| A.18 | IRQ7 | B.18 | AEXT5 | C.18 | IRQ0 |

| A.19 | HALT | B.19 | AEXT6 | C.19 | IRQ1 |

| A.20 | AB8 | B.20 | AEXT7 | C.20 | IRQ2 |

| A.21 | AB9 | B.21 | Reserved | C.21 | DB8 |

| A.22 | AB10 | B.22 | RSTHOLD | C.22 | DB9 |

| A.23 | AB11 | B.23 | Reserved | C.23 | DB10 |

| A.24 | AB12 | B.24 | IODEV1XX | C.24 | DB11 |

| A.25 | AB13 | B.25 | IODEV2XX | C.25 | DB12 |

| A.26 | AB14 | B.26 | IODEV3XX | C.26 | DB13 |

| A.27 | AB15 | B.27 | T34 | C.27 | DB14 |

| A.28 | SYSDEV | B.28 | CLK4 | C.28 | DB15 |

| A.29 | CLK1 | B.29 | CLK3 | C.29 | IRQ |

| A.30 | IRQS | B.30 | CLK2 | C.30 | RESET |

| A.31 | GND | B.31 | GND | C.31 | GND |

| A.32 | Vcc (+5V) | B.32 | Vcc (+5V) | C.32 | Vcc (+5V) |

B3.4.1. Compatible Connectors

The backplane receptacles are three-row, 32-pin per row DIN 41612 sockets. These can mate with the more expensive 96-pin plugs, but also with the cheaper 64-pin ones that only have rows A and C.

Row B contains signals necessary for the more unusual cards (expanded memory cards and processor extensions), so that most peripherals can have a cheaper connector. This doesn't save that much money, but it was easy to do and it makes me seem like I really know what I'm doing.

B3.4.2. Power Rails

The backplane carries power on 18 pins because it was made for TTL logic. CMOS logic needs less power, but hey, a healthy power supply is a prerequisite for something as complex as the CFT so I'm not complaining!

Ground, being the most important rail occupies half of these pins. All of rows 1, 2, and 31 are dedicated to it.

Vcc, which is a 5 V supply on the CFT, is given all the pins on rows 3 and 32.

An additional 3.3 V supply is on the three remaining pins on row 4. The only peripheral currently using that supply is the VDU board.

B3.4.3. The Address Bus

The Address Bus is 16 bits wide, and is exactly what anyone might expect. It carries the memory or I/O address to be read from or written to. To make card wiring easier, the bus is split into two 8-bit groups. The least significant group, AB0–7, is on the eight pins A.5–12. The most significant group, AB8–15, is on the eight pins A.20–27.

B3.4.4. The Address Expansion Bus

Like the Address Bus, this bus is unidirectional. Unlike the Address Bus, it's only driven during memory transactions. The unit responsible for it is the MBU, which generates extended addresses to allow the CFT to use up to 2 MW of memory.

A device that uses extended addressing must combine the AB0–12 and AEXT0–7 to form a 21-bit physical memory address, with AEXT7 as the most significant bit. With the MBU enabled, AB13–15 no longer address memory, they are a memory bank index and shouldn't be use.

The CFT's memory card uses this scheme.

The Address Expansion Bus is available on pins B.13–20.

B3.4.5. The Data Bus

The Data Bus is a bidirectional bus. When the processor needs to read from memory or I/O, the bus should be driven by exactly one peripheral. When the processor needs to write to memory or I/O, it drives the bus itself. The bus direction can be gleaned from R and W.

Like the Address Bus, I've split this bus into two 8-bit groups to ease card wiring and layout. The least significant group, DB0–7, is on the eight pins C.5–12. The most significant group, DB8–15, is on the eight pins A.21–28.

B3.4.6. Memory and I/O Transactions

- MEM (C.13)

- Output from the Microcode Store. When asserted, it indicates the Address Bus is being driven with a memory space address.

- IO (C.14)

- Output from the Microcode Store. When asserted, it indicates the Address Bus is being driven with an I/O space address.

- R (C.15)

- Output from the Microcode Store. When asserted, it indicates a memory or I/O read cycle is in progress. Any addressed devices should place on the Data Bus the data specified on the Address Bus.

- W (C.16)

- Output from the Microcode Store. When asserted, it indicates the data on the Data Bus should be written to memory or I/O space at the address currently on the Address Bus.

- SYSDEV (A.28)

- Output from the I/O Space Decoder. When asserted, it indicates this transaction is an I/O space one, and the Address Bus holds an address in the range 000–0FF. This is used to simplify decoding peripheral addresses as the top eight bits of the Address Bus are decoded by the processor.

- IODEV1XX (B.24)

- Output from the I/O Space Decoder. When asserted, it indicates this transaction is an I/O space one, and the Address Bus holds an address in the range 100–1FF.

- IODEV2XX (B.25)

- Output from the I/O Space Decoder. When asserted, it indicates this transaction is an I/O space one, and the Address Bus holds an address in the range 200–1FF.

- IODEV3XX (B.26)

- Output from the I/O Space Decoder. When asserted, it indicates this transaction is an I/O space one, and the Address Bus holds an address in the range 300–1FF.

B3.4.7. Interrupts

- IRQ (C.29)

- Open Drain input to the processor. A low level is used to signal an interrupt. On an unexpanded system, any expansion card may use this signal. An expanded system contains an interrupt controller card which handles the signalling.

- IRQ0, IRQ1, IRQ2, IRQ3, IRQ4, IRQ5, IRQ6, IRQ7, (C.18–20, A.13–16, A.18)

- Open Drain inputs to the Interrupt Controller card. Allows prioritised interrupt requests (IRQ0 is the highest priority). Note that these signals never reach the processor without this card.

- IRQS (A.30)

- Output from the processor. Indicates an interrupt has been seen and is about to be serviced. Use as an Interrupt Acknowledge signal.

B3.4.8. Other Signals

- RESET (C.30)

- Open Drain input to the processor and all devices. May be signalled by any device for the benefit of all others. Triggers a complete reset of the system.

- RSTHOLD (B.22)

- Output from the processor to all devices. Becomes asserted (low) when a reset is in progress, and remains asserted for a relatively long time. This may be used by devices that require a very long reset pulse.

- HALT (A.19)

- Open Drain input to the processor. When asserted, the processor stops operating and tri-states the IBUS, Data Bus (DBUS) and Address Bus as well as most control signals.

- CLK1, CLK2, CLK3, CLK4, T34 (A.29, B.28–B.30, B.27)

- These outputs from the clock generator carry all four 75% duty cycle phases of the system clock, plus the 50% duty cycle one.

- SKIPEXT (B.6)

- Open Drain input to the processor. This allows a peripheral to cause the next instruction to be skipped during the execution of an IOT instruction. This scheme is used to build processor extension boards.

- ENDEXT (B.7)

- Open Drain input to the processor. This allows a peripheral to cause the immediate end of the instruction currently executed. This is used to build processor extension boards.

- WS (B.8)

- Open Drain input to the processor. Asserting this signal during a memory or I/O space transaction prolongs the transaction by whole numbers of processor cycles. This slows the processor down for particularly slow devices.

- R1, R6, and R7 (B.8–9, B.10)

- Outputs from the processor. Used to address up to three future processor units for reading. When selected, the unit should place the value to be read onto the IBUS.

B3.5. Bus Transactions

Here are some example transactions using the CFT Expansion Bus.

B3.5.1. Memory Read

To initiate a memory read, the processor will assert MEM and R simultaneously. At that point, the AB will already be set up and hold a valid memory address. If the MBU is available and enabled, AEXT will also be valid, although a little delayed compared to AB.

Memory-mapped peripherals may use one of two addressing schemes:

- Use unexpanded memory addresses by decoding just the 16 bits in AB.

- Use expanded memory addresses by decoding a vector created by AEXT and AB0–12.

All memory-mapped peripherals on the bus should use the same scheme.

The addressed device should drive DB with the value at that address when both MEM and R are low. The read cycle lasts for 250 ns, so there's plenty of time for this. A wait state may be asserted if the memory-mapped peripheral needs even longer than this.

Memory read waveforms.

B3.5.2. I/O Space Read

To initiate an I/O space read, the processor will assert IO and R simultaneously. At that point, the AB will already be set up and hold a valid memory address.

The addressed device should drive DB with the value at that I/O address when both IO and R are low. The read cycle lasts for 250 ns, so there's plenty of time for this. A wait state may be asserted if the device needs longer.

Memory write waveforms.

B3.5.3. Memory Write

To initiate a memory write, the processor will assert MEM. R will be deasserted. At that point, the AB will already be set up and hold a valid memory address. If the MBU is available and enabled, AEXT will also be valid, although a little delayed compared to AB. A short pulse of W will signal the write.

Memory mapped peripherals may use one of two addressing schemes:

- Use unexpanded memory addresses by decoding just the 16 bits in AB.

- Use expanded memory addresses by decoding a vector created by AEXT and AB0–12.

All memory mapped peripherals on the bus should use the same scheme.

The addressed device can either:

DB is guaranteed to hold valid data before the W pulse.

Memory write waveforms.

B3.5.4. I/O Space Write

To initiate an I/O space write, the processor will assert IO. R will be deasserted. At that point, the AB will already be set up and hold a valid memory address. The addressed device can either:

DB is guaranteed to hold valid data before the W pulse. If a device needs longer than about 200 ns to handle this transaction, it may request a wait state.

I/O write waveforms.

B3.5.5. Read with Wait State

A slow device may assert the open drain signal WS early in a memory or I/O space read transaction to cause the processor to prolong the transaction by a whole number of 250 ns processor cycles. WS can be asserted at any point in the transaction, but the processor only registers it while T34 is low. It will then hold MEM (or IO), R, AB, AEXT, and DB (and in fact all signals and state) until WS has been deasserted and T34 goes low. If WS is still asserted (or asserted again) when next T34 goes low, the processor remains in the wait state.

Memory read waveforms with a wait state.

B3.5.6. Write with Wait State

A slow device may assert the open drain signal WS early in a memory or I/O space write transaction to cause the processor to prolong the transaction by a whole number of 250 ns processor cycles. WS can be asserted at any point in the transaction, but the processor only registers it while T34 is low. It will then hold MEM (or IO), R (deasserted), AB, AEXT, and DB until WS has been deasserted and T34 goes low. During this time, W will strobe once per processor cycle. It is up to the I/O space peripheral to handle this repeated pulse gracefully using some local state machine. If WS is still asserted (or asserted again) when next T34 goes low, the processor remains in the wait state.

Memory write waveforms with a wait state.